- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4277 > XC2S200-5FGG456C (Xilinx Inc)IC SPARTAN-II FPGA 200K 456-FBGA PDF資料下載

參數(shù)資料

| 型號: | XC2S200-5FGG456C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 4/99頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 200K 456-FBGA |

| 標準包裝: | 60 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計: | 57344 |

| 輸入/輸出數(shù): | 284 |

| 門數(shù): | 200000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 456-BBGA |

| 供應(yīng)商設(shè)備封裝: | 456-FBGA |

| 其它名稱: | 122-1312 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

12

R

Local Routing

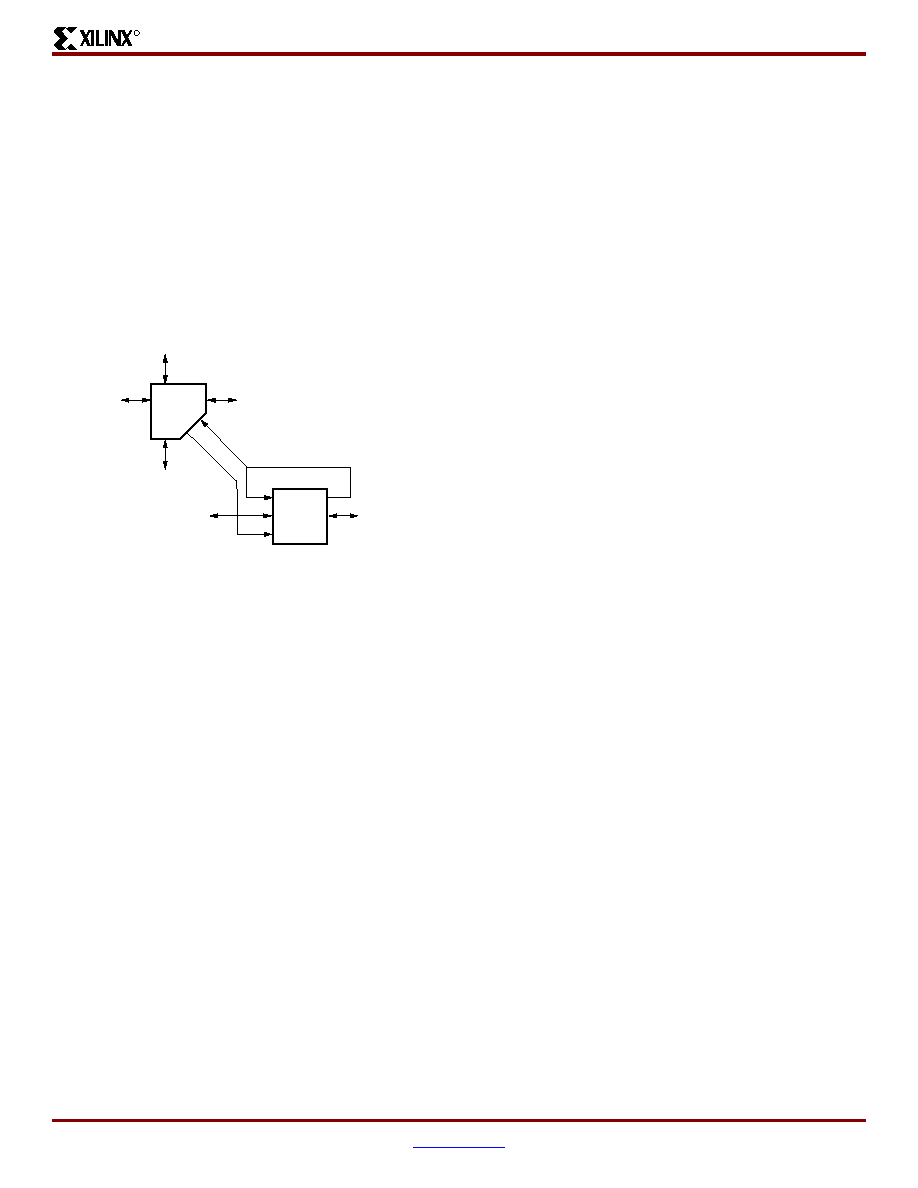

The local routing resources, as shown in Figure 6, provide

the following three types of connections:

Interconnections among the LUTs, flip-flops, and

General Routing Matrix (GRM)

Internal CLB feedback paths that provide high-speed

connections to LUTs within the same CLB, chaining

them together with minimal routing delay

Direct paths that provide high-speed connections

between horizontally adjacent CLBs, eliminating the

delay of the GRM

General Purpose Routing

Most Spartan-II FPGA signals are routed on the general

purpose routing, and consequently, the majority of

interconnect resources are associated with this level of the

routing hierarchy. The general routing resources are

located in horizontal and vertical routing channels

associated with the rows and columns CLBs. The

general-purpose routing resources are listed below.

Adjacent to each CLB is a General Routing Matrix

(GRM). The GRM is the switch matrix through which

horizontal and vertical routing resources connect, and

is also the means by which the CLB gains access to

the general purpose routing.

24 single-length lines route GRM signals to adjacent

GRMs in each of the four directions.

96 buffered Hex lines route GRM signals to other

GRMs six blocks away in each one of the four

directions. Organized in a staggered pattern, Hex lines

may be driven only at their endpoints. Hex-line signals

can be accessed either at the endpoints or at the

midpoint (three blocks from the source). One third of

the Hex lines are bidirectional, while the remaining

ones are unidirectional.

12 Longlines are buffered, bidirectional wires that

distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the

device, and horizontal ones span the full width of the

device.

I/O Routing

Spartan-II devices have additional routing resources

around their periphery that form an interface between the

CLB array and the IOBs. This additional routing, called the

VersaRing, facilitates pin-swapping and pin-locking, such

that logic redesigns can adapt to existing PCB layouts.

Time-to-market is reduced, since PCBs and other system

components can be manufactured while the logic design is

still in progress.

Dedicated Routing

Some classes of signal require dedicated routing resources

to maximize performance. In the Spartan-II architecture,

dedicated routing resources are provided for two classes of

signal.

Horizontal routing resources are provided for on-chip

3-state busses. Four partitionable bus lines are

provided per CLB row, permitting multiple busses

within a row, as shown in Figure 7.

Two dedicated nets per CLB propagate carry signals

vertically to the adjacent CLB.

Global Routing

Global Routing resources distribute clocks and other

signals with very high fanout throughout the device.

Spartan-II devices include two tiers of global routing

resources referred to as primary and secondary global

routing resources.

The

primary

global

routing

resources

are

four

dedicated global nets with dedicated input pins that are

designed to distribute high-fanout clock signals with

minimal skew. Each global clock net can drive all CLB,

IOB, and block RAM clock pins. The primary global

nets may only be driven by global buffers. There are

four global buffers, one for each global net.

The secondary global routing resources consist of 24

backbone lines, 12 across the top of the chip and 12

across bottom. From these lines, up to 12 unique

signals per column can be distributed via the 12

longlines in the column. These secondary resources

are more flexible than the primary resources since they

are not restricted to routing only to clock pins.

Figure 6: Spartan-II Local Routing

DS001_06_032300

CLB

GRM

To

Adjacent

GRM

To Adjacent

GRM

Direct

Connection

To Adjacent

CLB

To Adjacent

GRM

To Adjacent

GRM

Direct Connection

To Adjacent

CLB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 745777-4 | CONN D-SUB GASKET RFI 37POS TIN |

| 24LC32AFT-E/MNY | IC SRL EEPROM 4KX8 2.5V 8-TDFN |

| XC3S700A-4FG400I | IC SPARTAN-3A FPGA 700K 400FBGA |

| 554043-2 | CONN STANDOFF M3.5 SCKT #6-32 |

| 24LC64FT-E/SN | IC SRL EEPROM 8KX8 2.5V 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200-5FGG456C4124 | 制造商:Xilinx 功能描述: |

| XC2S200-5FGG456I | 功能描述:IC SPARTAN-II FPGA 200K 456-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208C | 功能描述:IC FPGA 2.5V 1176 CLB'S 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208I | 功能描述:IC FPGA 2.5V I-TEMP 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208Q | 制造商:Xilinx 功能描述:XILINX XC2S200-5PQ208Q FPGA - Trays 制造商:Xilinx 功能描述:Xilinx XC2S200-5PQ208Q FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。