- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4277 > XC2S150-6FG456C (Xilinx Inc)IC FPGA 2.5V C-TEMP 456-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S150-6FG456C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 3/99頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 2.5V C-TEMP 456-FBGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 864 |

| 邏輯元件/單元數(shù): | 3888 |

| RAM 位總計(jì): | 49152 |

| 輸入/輸出數(shù): | 260 |

| 門(mén)數(shù): | 150000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 456-BBGA |

| 供應(yīng)商設(shè)備封裝: | 456-FBGA |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

11

R

Similarly, the F6 multiplexer combines the outputs of all four

function generators in the CLB by selecting one of the

F5-multiplexer outputs. This permits the implementation of

any 6-input function, an 8:1 multiplexer, or selected

functions of up to 19 inputs.

Each CLB has four direct feedthrough paths, one per LC.

These paths provide extra data input lines or additional

local routing that does not consume logic resources.

Arithmetic Logic

Dedicated carry logic provides capability for high-speed

arithmetic functions. The Spartan-II FPGA CLB supports

two separate carry chains, one per slice. The height of the

carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a

1-bit full adder to be implemented within an LC. In addition,

a dedicated AND gate improves the efficiency of multiplier

implementation.

The dedicated carry path can also be used to cascade

function generators for implementing wide logic functions.

BUFTs

Each Spartan-II FPGA CLB contains two 3-state drivers

(BUFTs) that can drive on-chip busses. See "Dedicated

Routing," page 12. Each Spartan-II FPGA BUFT has an

independent 3-state control pin and an independent input

pin.

Block RAM

Spartan-II FPGAs incorporate several large block RAM

memories. These complement the distributed RAM

Look-Up Tables (LUTs) that provide shallow memory

structures implemented in CLBs.

Block RAM memory blocks are organized in columns. All

Spartan-II devices contain two such columns, one along

each vertical edge. These columns extend the full height of

the chip. Each memory block is four CLBs high, and

consequently, a Spartan-II device eight CLBs high will

contain two memory blocks per column, and a total of four

blocks.

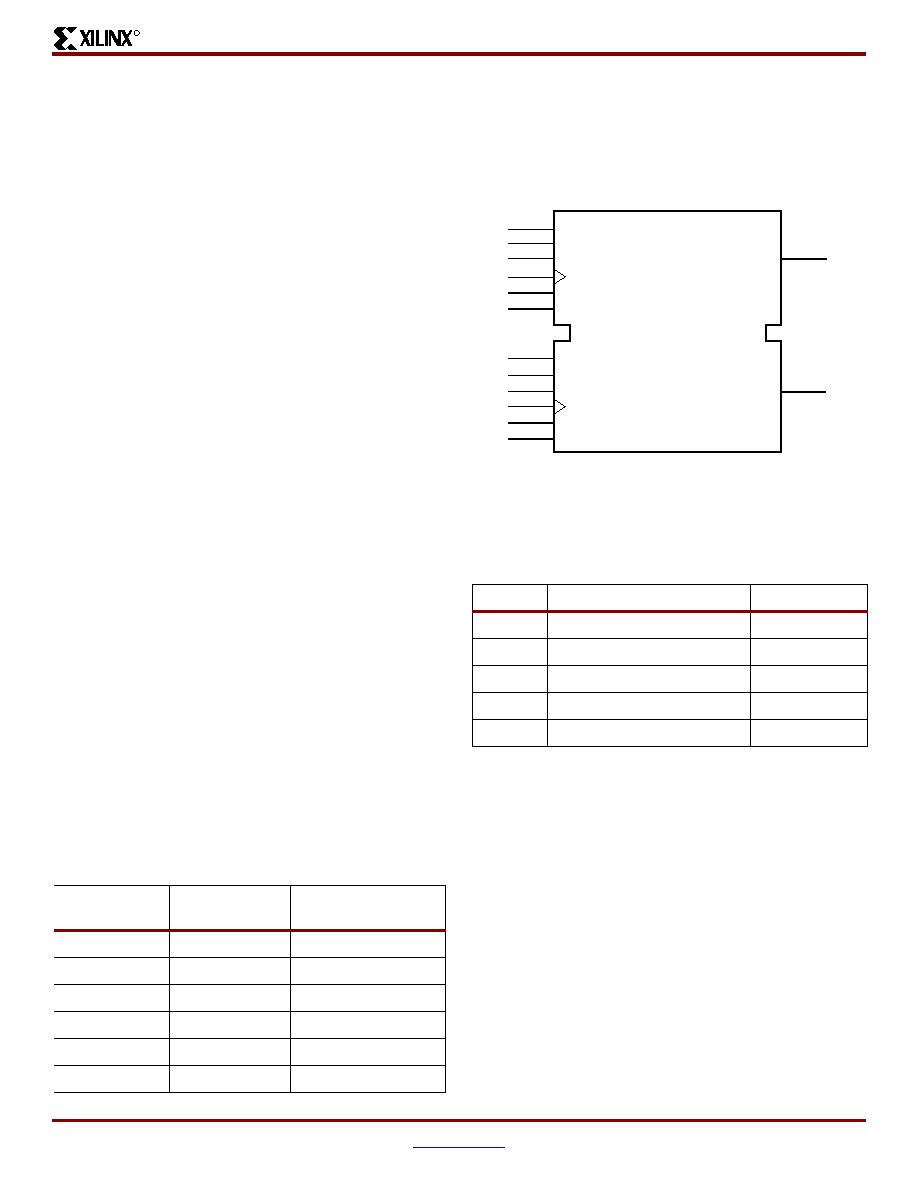

Each block RAM cell, as illustrated in Figure 5, is a fully

synchronous dual-ported 4096-bit RAM with independent

control signals for each port. The data widths of the two

ports can be configured independently, providing built-in

bus-width conversion.

Table 6 shows the depth and width aspect ratios for the

block RAM.

The Spartan-II FPGA block RAM also includes dedicated

routing to provide an efficient interface with both CLBs and

other block RAMs.

Programmable Routing Matrix

It is the longest delay path that limits the speed of any

worst-case design. Consequently, the Spartan-II routing

architecture and its place-and-route software were defined

in a single optimization process. This joint optimization

minimizes long-path delays, and consequently, yields the

best system performance.

The joint optimization also reduces design compilation

times because the architecture is software-friendly. Design

cycles are correspondingly reduced due to shorter design

iteration times.

Table 5: Spartan-II Block RAM Amounts

Spartan-II

Device

# of Blocks

Total Block RAM

Bits

XC2S15

4

16K

XC2S30

6

24K

XC2S50

8

32K

XC2S100

10

40K

XC2S150

12

48K

XC2S200

14

56K

Figure 5: Dual-Port Block RAM

Table 6: Block RAM Port Aspect Ratios

Width

Depth

ADDR Bus

Data Bus

1

4096

ADDR<11:0>

DATA<0>

2

2048

ADDR<10:0>

DATA<1:0>

4

1024

ADDR<9:0>

DATA<3:0>

8

512

ADDR<8:0>

DATA<7:0>

16

256

ADDR<7:0>

DATA<15:0>

WEB

ENB

RSTB

CLKB

ADDRB[#:0]

DIB[#:0]

WEA

ENA

RSTA

CLKA

ADD[#:0]

DIA[#:0]

DOA[#:0]

DOB[#:0]

RAMB4_S#_S#

DS001_05_060100

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 745530-3 | CONN BACK COVER SLIDE ON DB25 |

| 93AA86A-I/MS | IC EEPROM 16KBIT 2048X8 8-MSOP |

| XC2S150-5FG456I | IC FPGA 2.5V I-TEMP 456-FBGA |

| XC3S500E-4FG320I | IC FPGA SPARTAN 3E 320FBGA |

| 25LC040AT-I/MNY | IC EEPROM SER 4K 512X8 8TDFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S150-6FG456I | 制造商:Xilinx 功能描述: |

| XC2S150-6FGG256C | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 150K GATES 3888 CELLS 263MHZ 2.5V 256FBGA - Trays 制造商:Xilinx 功能描述:FPGA, 864 CLBS, 150000 GATES, 263 MHz, PBGA256 |

| XC2S150-6FGG256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S150-6FGG456C | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 150K GATES 3888 CELLS 263MHZ 2.5V 456FBGA - Trays 制造商:Xilinx 功能描述:IC FPGA 260 I/O 456FBGA 制造商:Xilinx 功能描述:IC FPGA SPARTAN-2C 150K 456FBGA |

| XC2S150-6FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。