- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄376449 > X98024 (Intersil Corporation) 240MHz Triple Video Digitizer with Digital PLL PDF資料下載

參數(shù)資料

| 型號(hào): | X98024 |

| 廠商: | Intersil Corporation |

| 英文描述: | 240MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | 240MHz的三路視頻數(shù)字化與數(shù)字鎖相環(huán) |

| 文件頁(yè)數(shù): | 13/29頁(yè) |

| 文件大小: | 295K |

| 代理商: | X98024 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

13

FN8220.0

June 6, 2005

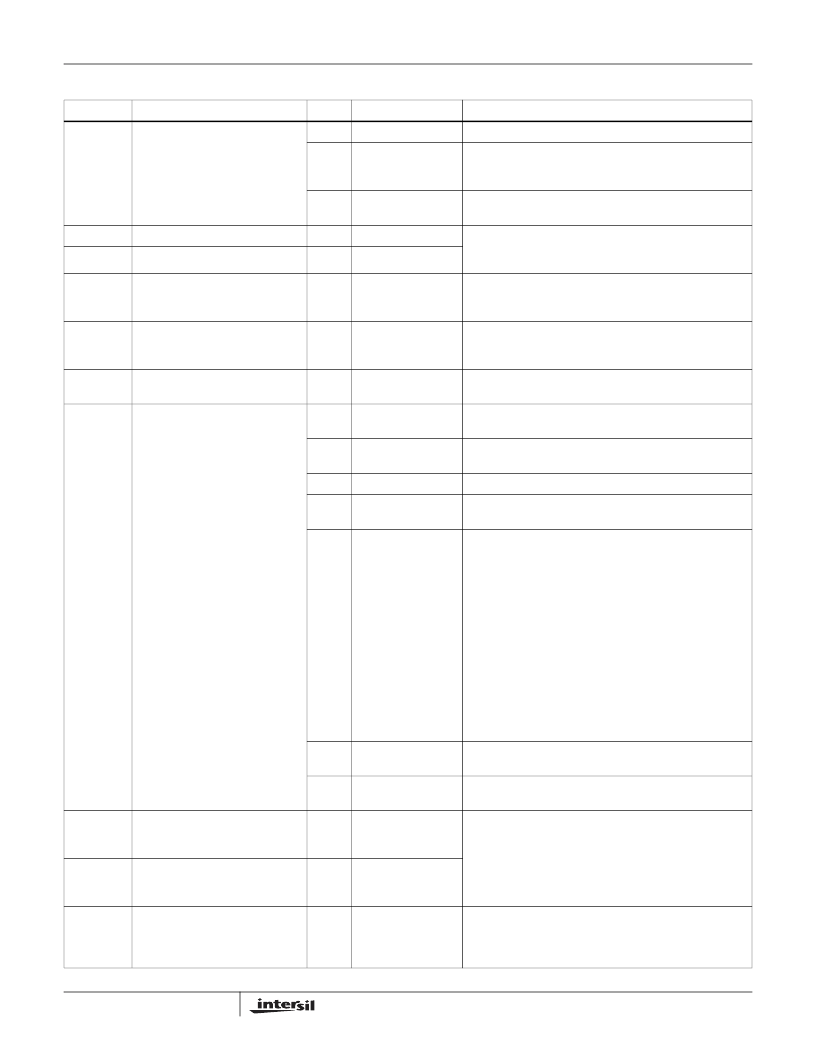

0x0D

AFE Bandwidth (0x0E)

0

Unused

Value doesn’t matter

3:1

AFE BW

3dB point for AFE lowpass filter

000: 100MHz

111: 780MHz (default)

7:4

Peaking

0000: Disabled (default) See

Bandwidth and Peaking

Control

section for more information

0x0E

PLL Htotal MSB (0x03)

5:0

PLL Htotal MSB

14 bit HTOTAL (number of active pixels) value

The minimum HTOTAL value supported is 0x200.

HTOTAL to PLL is updated on LSB write only.

0x0F

PLL Htotal LSB (0x20)

7:0

PLL Htotal LSB

0x10

PLL Sampling Phase (0x00)

5:0

PLL Sampling Phase

Used to control the phase of the ADC’s sample point relative

to the period of a pixel. Adjust to obtain optimum image

quality. One step = 5.625° (1.56% of pixel period).

0x11

PLL Pre-coast (0x08)

7:0

Pre-coast

Number of lines the PLL will coast prior to the start of

VSYNC. Applies only to internally generated COAST

signals.

0x12

PLL Post-coast (0x00)

7:0

Post-coast

Number of lines the PLL will coast after the end of VSYNC.

Applies only to internally generated COAST signals.

0x13

PLL Misc (0x00)

0

PLL Lock Edge

HSYNC1

0: Lock on trailing edge of HSYNC1 (default)

1: Lock on leading edge of HSYNC1

1

PLL Lock Edge

HSYNC2

0: Lock on trailing edge of HSYNC2 (default)

1: Lock on leading edge of HSYNC2

2

Reserved

Set to 0.

3

CLKINV

IN

Pin

Disable

0: CLKINV

IN

pin enabled (default)

1: CLKINV

IN

pin disabled (internally forced low)

5:4

CLKINV

IN

Pin

Function

00: CLKINV (default)

01: External CLAMP (see Note)

10: External COAST

11: External PIXCLK

Note: the CLAMP pulse is used to

- perform a DC restore (if enabled)

- start the ABLC function (if enabled), and

- update the data to the Offset DACs (always).

When in the default internal CLAMP mode, the X98024

automatically generates the CLAMP pulse. If External

CLAMP is selected, the Offset DAC values will only change

on the leading edge of CLAMP. If there is no internal clamp

signal, there will be up to a 100ms delay between when the

PGA gain or offset DAC register is written to, and when the

PGA or offset DAC is actually updated.

6

XTALCLKOUT

Frequency

0: XTALCLK

OUT

= f

CRYSTAL

(default)

1: XTALCLK

OUT

= f

CRYSTAL

/2

7

Disable

XTALCLKOUT

0 = XTALCLK

OUT

enabled

1 = XTALCLK

OUT

is logic low

0x14

DC Restore and ABLC starting

pixel MSB (0x00)

4:0

DC Restore and

ABLC starting

pixel (MSB)

Pixel after HSYNC

IN

trailing edge to begin

DC restore and ABLC functions. 13 bits.

Set this register to the first stable black pixel following the

trailing edge of HSYNC

IN

.

0x15

DC Restore and ABLC starting

pixel LSB (0x00)

7:0

DC Restore and

ABLC starting

pixel (LSB)

0x16

DC Restore Clamp Width

(0x10)

7:0

DC Restore clamp

width (pixels)

Width of DC restore clamp used in AC-coupled

configurations. Has no effect on ABLC. Minimum value is

0x02 (a setting of 0x01 or 0x00 will not generate a clamp

pulse).

Register Listing

(Continued)

ADDRESS

REGISTER (DEFAULT VALUE)

BIT(s)

FUNCTION NAME

DESCRIPTION

X98024

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

| XC145481DW | 3 V PCM Codec-Filter |

| XC145481P | 3 V PCM Codec-Filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X98024_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 標(biāo)準(zhǔn)包裝:250 系列:- 類型:電平移位器 應(yīng)用:LCD 電視機(jī)/監(jiān)控器 安裝類型:表面貼裝 封裝/外殼:28-WFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:28-WQFN(4x4)裸露焊盤(pán) 包裝:帶卷 (TR) 其它名稱:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

| X98027_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:275MHz Triple Video Digitizer with Digital PLL |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。