- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371269 > X68C75J Port Expander and E2 Memory PDF資料下載

參數(shù)資料

| 型號: | X68C75J |

| 英文描述: | Port Expander and E2 Memory |

| 中文描述: | 端口擴展和E2內(nèi)存 |

| 文件頁數(shù): | 9/26頁 |

| 文件大小: | 123K |

| 代理商: | X68C75J |

9

X68C75 SLIC

E

2

The complemented contents of the SFR map register

and the E

2

memory map register can be read by the

microcontroller at their corresponding SFR addresses.

The physical memory location of these registers can be

derived by adding the following offset to the SFR base

address:

SFR Map Register

E

2

Memory Map Register

00H

38H

If the regions specified in the map registers overlap, only

the SFR will be accessible.

Interrupt Status Register (ISR)

The Interrupt Status Register is a volatile register used

to configure the interrupt condition for the I/O ports as

well as to determine the interrupt status of the ports. The

X68C75 ports can generate an interrupt to the microcon-

troller upon the proper transition (as specified in the

configuration register) on either STRA or STRB pins

when the corresponding I/O port is configured as an

input.

The INT flag is set when any of input strobes are toggled

provided that their corresponding interrupt enable bits

(ENA, ENB) are set. The INT flag is cleared when

latched data is read (PDR ) or pending interrupt status

flag (INTA, INTB) in ISR is forced to “0” by the interrupt

service routine. Interrupt service routine should exam-

ine the interrupt status flags (INTA, INTB) and identify

the source of pending interrupt.

The E

2

memory interrupt status flag (EOW) is another

means to detect the early completion of a write cycle.

When ENEE is enabled, the hardware will set the EOW

flag, and interrupt the microcontroller at the end of an

internal programming cycle. Toggle Bit Polling can be

replaced by the EOW hardware interrupt, which reduces

the software overhead. The EOW flag should be cleared

by software. The interrupt status register bits are mapped

as follows.

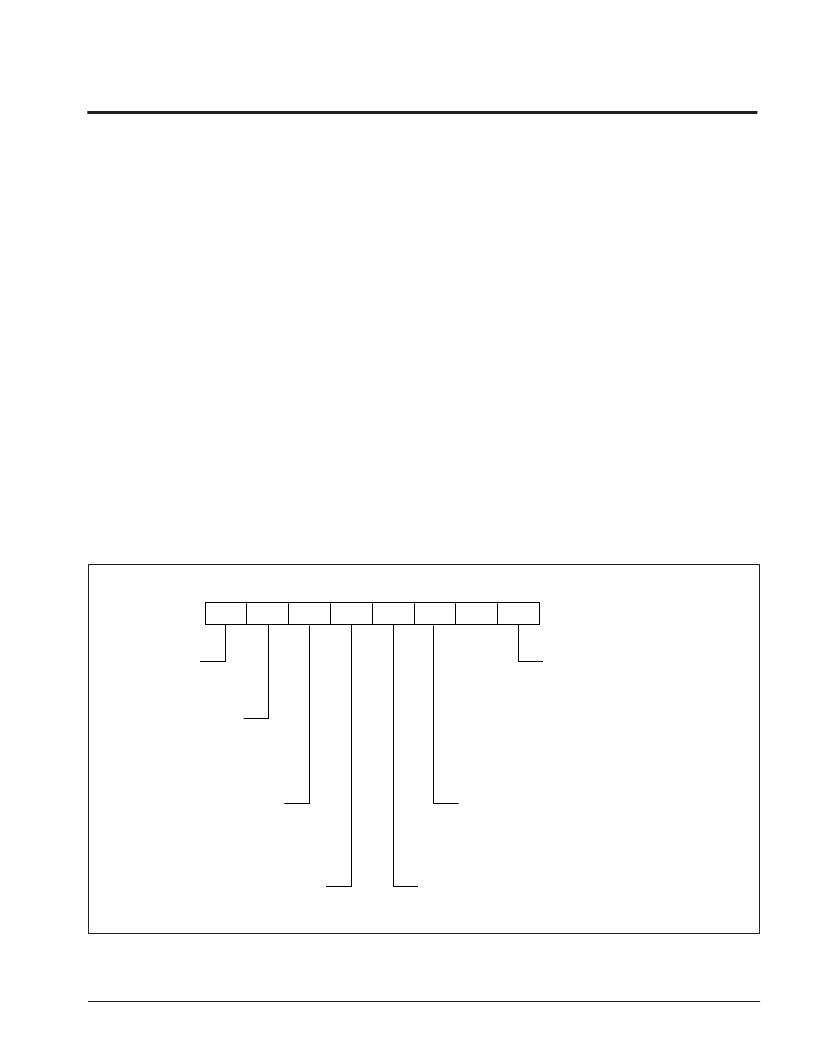

Figure 10. Interrupt Status Register

INT

2899 ILL F12.1

INTA INTB

ENA

ENB ENEE

0

EOW

7

6

5

4

3

2

1

0

Interrupt Flag

“0” = No pending interrupt

“1” = Interrupt request

Port B – Interrupt Status

“0” = No pending interrupt

“1” = Port B latched data when a valid

transition occurred on the STRB

and port B was an input port.

Port A – Interrupt Enable

“0” = Mask off interrupt

“1” = Interrupt enabled

Port B – Interrupt Enable

“0” = Mask off interrupt

“1” = Interrupt enabled

EEPROM Interrupt Enable

“0” = Mask off interrupt

“1” = Interrupt enabled

EEPROM Interrupt Status

“0” = Programming in progress

“1” = Set by hardware when it completes

programming the previously

written data

Port A – Interrupt Status

“0” = No pending interrupt

“1” = Port A latched data when a valid

transition occurred on the STRA

and port A was an input port.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X68C75JI | Port Expander and E2 Memory |

| X68C75JM | Port Expander and E2 Memory |

| X68C75L | Port Expander and E2 Memory |

| X68C75LI | Port Expander and E2 Memory |

| X68C75LM | Port Expander and E2 Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X68C75JI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75JM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75L | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75LI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75LM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復。