- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359428 > VSC7135 (Vitesse Semiconductor Corporation.) 1.25Gbits/sec Gigabit Ethernet Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | VSC7135 |

| 廠商: | Vitesse Semiconductor Corporation. |

| 英文描述: | 1.25Gbits/sec Gigabit Ethernet Transceiver |

| 中文描述: | 1.25Gbits/sec千兆以太網(wǎng)收發(fā)器 |

| 文件頁(yè)數(shù): | 2/16頁(yè) |

| 文件大小: | 138K |

| 代理商: | VSC7135 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

VITESSE

Data Sheet

VSC7135

1.25Gbits/sec

Gigabit Ethernet Transceiver

Page 2

VITESSE

SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 805/388-3700 FAX: 805/987-5896

5/28/98

G52146-0, Rev. 4.0

Functional Description

Clock Synthesizer

The VSC7135 clock synthesizer multiplies the reference frequency provided on the REFCLK pin by 10 to

achieve a baud rate clock at nominally 1.25GHz. The clock synthesizer contains a fully monolithic PLL which

does not require any external components.

Serializer

The VSC7135 accepts TTL input data as a parallel 10 bit character on the T0:9 bus which is latched into the

input latch on the rising edge of REFCLK. This data will be serialized and transmitted on the TX PECL differ-

ential outputs at a baud rate of ten times the frequency of the REFCLK input, with bit T0 transmitted first. User

data should be encoded for transmission using the 8B/10B block code described in the Fibre Channel specifica-

tion, or an equivalent, edge rich, DC-balanced code.

Transmission Character Interface

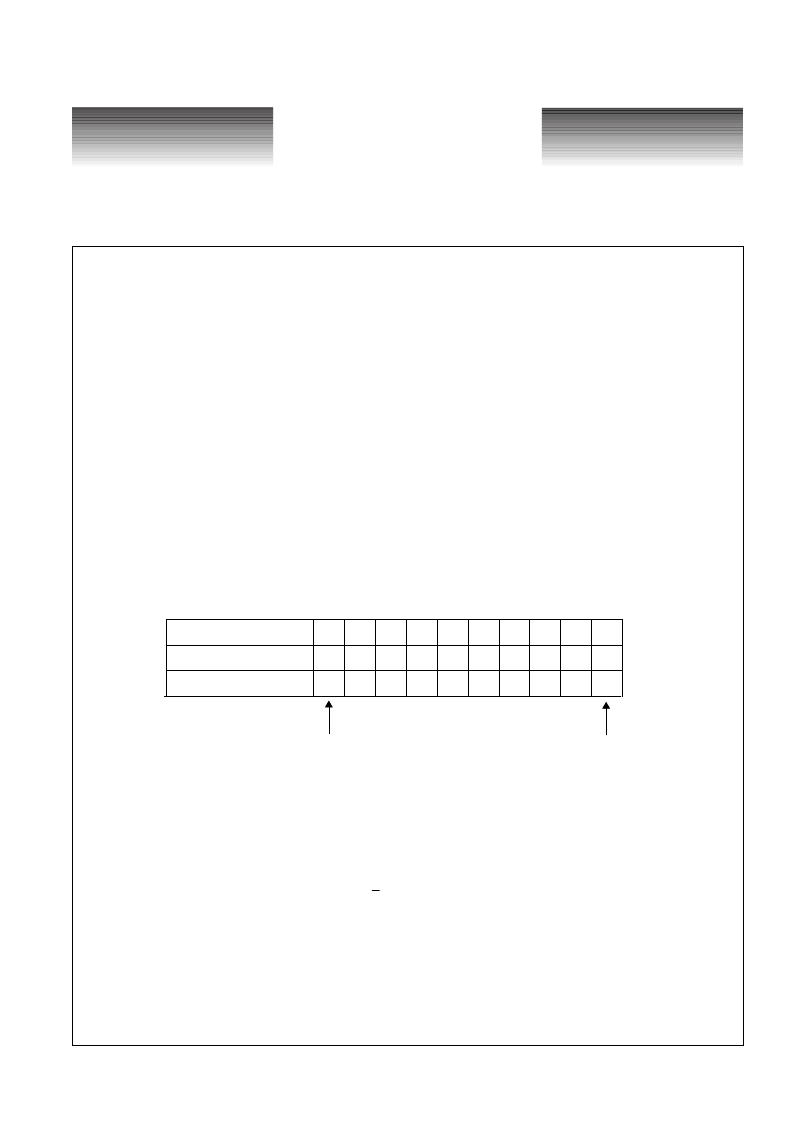

An encoded byte is 10 bits and is referred to as a transmission character. The 10 bit interface on the

VSC7135 corresponds to a transmission character. This mapping is illustrated in Figure 2.

Figure 1: Transmission Order and Mapping of an 8B/10B Character

Clock Recovery

The VSC7135 accepts differential high speed serial inputs on the RX+/RX- pins, extracts the clock and

retimes the data. The serial bit stream should be encoded so as to provide DC balance and limited run length by

an 8B/10B transmitter or equivalent. The VSC7135 clock recovery circuitry is completely monolithic and

requires no external components. For proper operation, the baud rate of the data stream to be recovered should

be within 0.01% of ten times the REFCLK frequency. For example if the REFCLK used is 125MHz, then the

incoming serial baud rate must be 1.25 gigabaud +0.01%.

Deserializer

The retimed serial bit stream is converted into a 10-bit parallel output character. The VSC7135 provides

complementary TTL recovered clocks, RCLK and RCLKN, which are at one-twentieth of the serial baud rate.

This architecture is designed to simplify demultiplexing of the 10-bit data characters into a 20-bit half-word in

the downstream controller chip. The clocks are generated by dividing down the high-speed clock which is phase

locked to the serial data. The serial data is retimed by the internal high-speed clock, and deserialized. The result-

First Data Bit Transmitted

Last Data Bit Transmitted

Parallel Data Bits

8B/10B Bit Position

T9

T8

T7

T6

T5

T4

T3

T2

T1

T0

j

h

g

f

i

e

d

c

b

a

Comma Character

X

X

X

1

1

1

1

1

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VSC7139 | Quad Transceiver for Gigabit Ethernet and Fibre Channel |

| VSC7140 | 1.0625 Gb/s Fibre Channel Dual Repeater / Hub Node |

| VSC7140QJ | 1.0625 Gb/s Fibre Channel Dual Repeater / Hub Node |

| VSC7142 | Dual Repeater/Retimer for Fibre Channel and Gigabit Ethernet |

| VSC7146 | BOX 4.94X2.75X1.275 W/CLP ALMOND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VSC7135QN | 制造商:Vitesse Semiconductor Corporation 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP |

| VSC7135QU | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:LAN Transceiver |

| VSC7139 | 制造商:VITESSE 制造商全稱(chēng):Vitesse Semiconductor Corporation 功能描述:Quad Transceiver for Gigabit Ethernet and Fibre Channel |

| VSC7139TW | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Telecomm/Datacomm |

| VSC7140 | 制造商:VITESSE 制造商全稱(chēng):Vitesse Semiconductor Corporation 功能描述:1.0625 Gb/s Fibre Channel Dual Repeater / Hub Node |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。