- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202172 > V59C1512164QCF3I (PROMOS TECHNOLOGIES INC) 32M X 16 DDR DRAM, 0.45 ns, PBGA84 PDF資料下載

參數(shù)資料

| 型號: | V59C1512164QCF3I |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 32M X 16 DDR DRAM, 0.45 ns, PBGA84 |

| 封裝: | ROHS COMPLIANT, MO-207, FBGA-84 |

| 文件頁數(shù): | 51/76頁 |

| 文件大小: | 1192K |

| 代理商: | V59C1512164QCF3I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

55

ProMOS TECHNOLOGIES

V59C1512(404/804/164)QC*I

V59C1512(404/804/164)QC*I Rev. 1.1 April 2008

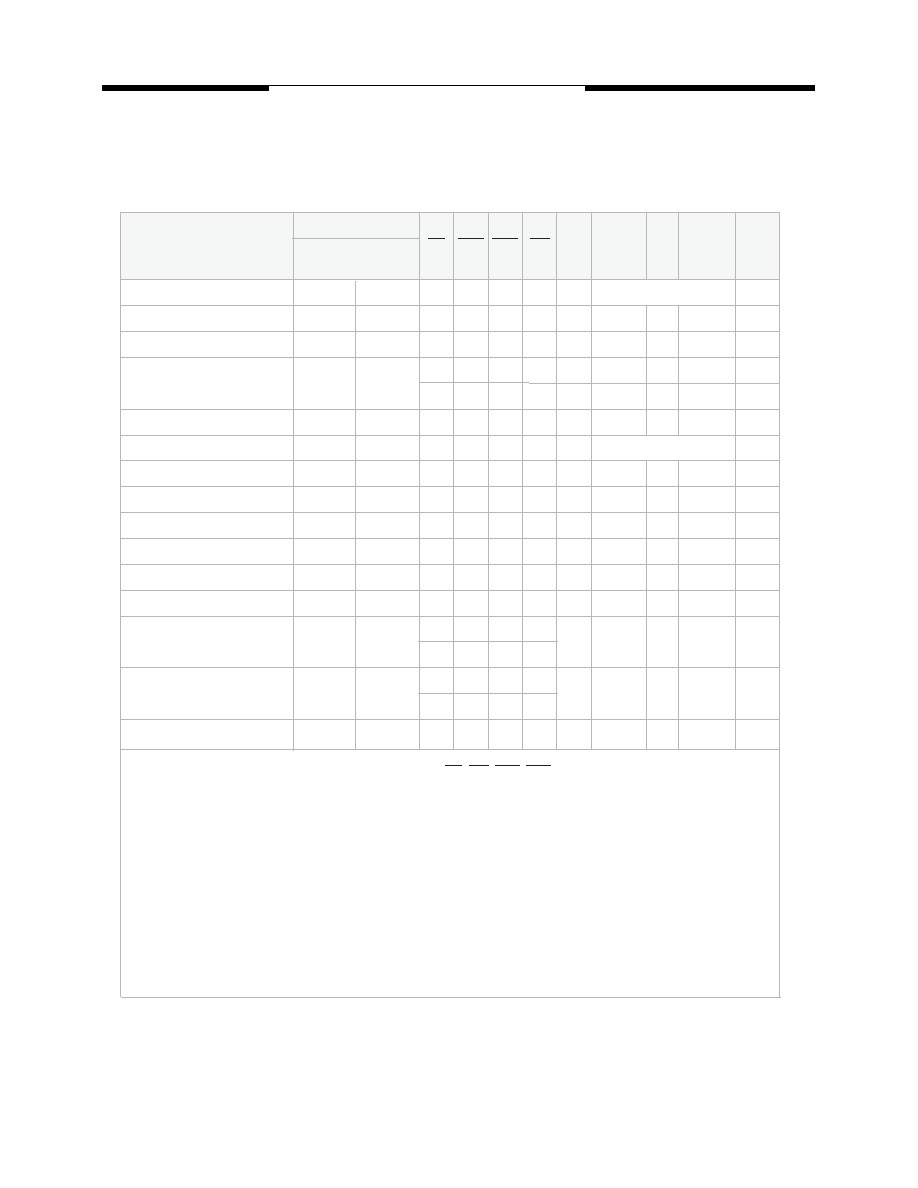

Truth Tables

Func tion

CKE

CS

RAS CAS

WE

BA0

BA1

A12-A11 A10

A9 - A0

Notes

Previo us

Cycle

Curre nt

Cycle

(Extended) Mode Register Set

H

L

LLL

BA

OP Code

1, 2

Auto-Refresh

HH

L

H

X

1

Self-Refresh Entry

HL

L

H

X

1

Self-Refresh Exit

L

H

X

XXX

X

1

LH

H

X

1

Precharge all Banks

HH

L

H

L

X

H

X

1

Bank Activate

H

L

H

BA

Row Address

1, 2

Write

H

L

H

L

BA

Column

L

Column

1,2,3

Write with Auto-Precharge

H

L

H

L

BA

Column

H

Column

1,2,3

Read

H

L

H

L

H

BA

Column

L

Column

1,2,3

Read with Auto-Precharge

HH

L

H

L

H

BA

Column

H

Column

1,2,3

No Operation

HX

L

H

X

1

Device Deselect

H

X

H

X

XXX

X

1

Power Down Entry

HL

HX

X

XX

X

1,4

LH

H

Power Down Exit

LH

HX

X

XX

X

1,4

LH

H

1. All DDR2 SDRAM commands are defined by states of CS, WE, RAS, CAS, and CKE at the rising edge of the clock.

2. Bank addresses (BA0, BA1) determine which bank is to be operated upon. For (E)MRS BA selects an (Extended)

Mode

Register.

3. Burst reads or writes at BL = 4 cannot be terminated. See sections “Reads interrupted by a Read” and “Writes inter-

rupted by a Write”.

4. The Power Down Mode does not perform any refresh operations. The duration of Power Down is therefore limited by

the refresh requirements.

5. The state of ODT does not affect the states decribed in this table. The ODT function is not available during Self

Refresh.

6. “X” means “H or L (but a defined logic level)”.

7. Operation that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM

must be powered down and then restartet through the specified initialization sequence before normal operation can

continue.

Command Truth Table

XX

Single Bank Precharge

HH

LL

H

L

X

L

X

BA

1, 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01168QBLJ-25I | DDR DRAM, PBGA84 |

| V59C1G01408QAUP25A | 256M X 4 DDR DRAM, PBGA68 |

| V59C1512164QALJ25AH | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QALP37I | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QAUJ5I | 32M X 16 DDR DRAM, PBGA92 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V59C1512164QDJ25 | 制造商:ProMOS 功能描述:32M*16 DDRII, 1.8V, BGA, 400MHz, Green Part 制造商:ProMOS Technologies INC. 功能描述:32M*16 DDRII, 1.8V, BGA, 400MHz, Green Part |

| V59C1512164QDJ25A | 制造商:ProMOS 功能描述:32M*16 DDRII, 1.8V, BGA, 800MHz, Green Part, CL6 制造商:ProMOS Technologies INC. 功能描述:32M*16 DDRII, 1.8V, BGA, 800MHz, Green Part, CL6 |

| V59C1512164QDJ25I | 制造商:ProMOS 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part, 制造商:ProMOS Technologies INC. 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part, |

| V59C1512164QDJ3 | 制造商:ProMOS 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part 制造商:ProMOS Technologies INC. 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part |

| V59C1512164QDJ3I | 制造商:ProMOS 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part, 制造商:ProMOS Technologies INC. 功能描述:32M*16 DDRII, 1.8V, BGA, 333MHz, Green Part, |

發(fā)布緊急采購,3分鐘左右您將得到回復。