- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄202172 > V58C2256804SHLT6E (PROMOS TECHNOLOGIES INC) 32M X 8 DDR DRAM, PDSO66 PDF資料下載

參數(shù)資料

| 型號(hào): | V58C2256804SHLT6E |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 32M X 8 DDR DRAM, PDSO66 |

| 封裝: | 0.400 INCH, PLASTIC, MS-024FC, TSOP2-66 |

| 文件頁(yè)數(shù): | 37/60頁(yè) |

| 文件大小: | 1125K |

| 代理商: | V58C2256804SHLT6E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

42

V58C2256(804/404/164)SH Rev. 1.1 July 2010

ProMOS TECHNOLOGIES

V58C2256(804/404/164)SH

NOTES: (continued)

43. Note 43 is not used.

44. During initialization, VDDQ, VTT, and VREF must be equal to or less than VDD + 0.3V. Alternatively, VTT may

be 1.35V maximum during power up, even if VDD /VDDQ are 0 volts, provided a minimum of 42 ohms of series

resistance is used between the VTT supply and the input pin.

45. Note 45 is not used.

46. tRAP t RCD.

47. Note 47 is not used.

48. Random addressing changing 50% of data changing at every transfer.

49. Random addressing changing 100% of data changing at every transfer.

50. CKE must be active (high) during the entire time a refresh command is executed. That is, from the time the AUTO

REFRESH command is registered, CKE must be active at each rising clock edge, until tREF later.

51. IDD2N specifies the DQ, DQS, and DM to be driven to a valid high or low logic level. IDD2Q is similar to IDD2F

except IDD2Q specifies the address and control inputs to remain stable. Although IDD2F, IDD2N, and IDD2Q are

similar, IDD2F is “worst case.”

52. Whenever the operating frequency is altered, not including jitter, the DLL is required to be reset. This is followed

by 200 clock cycles.

53. These parameters guarantee device timing, but they are not necessarily tested on each device. They may be

guaranteed by device design or tester correlation.

54. tDAL =(tWR/ tCK) + (tRP/ tCK)

For each of the terms above, if not already an integer, round to the next highest integer.

For example: For DDR266B at CL=2.5 and tCK=7.5ns

tDAL=((15ns /7.5ns) + (20ns/ 7.5ns)) clocks=((2)+(3)) clocks=5 clocks

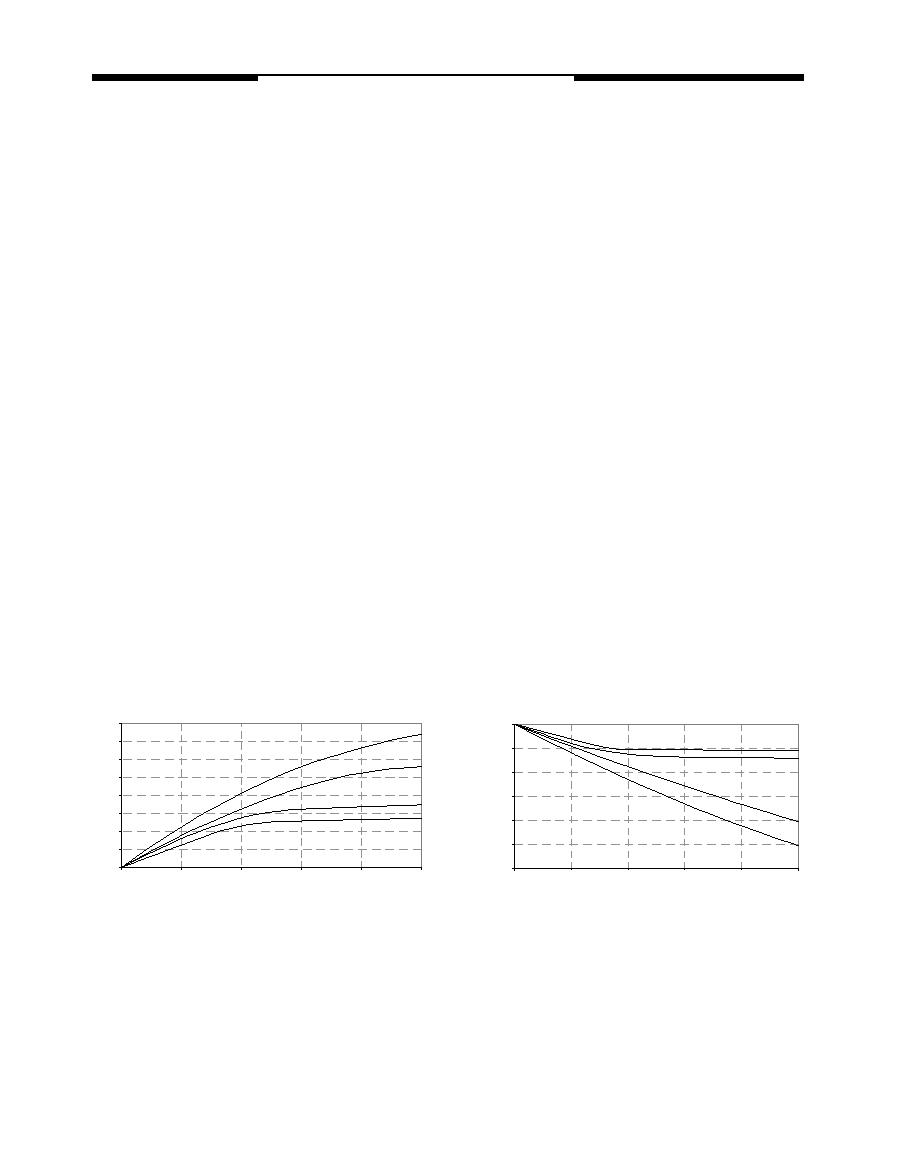

Max

imum

Nominal

high

Nominal low

Nominal

high

Minimum

Maxim

um

80

70

60

50

40

30

20

10

0.0

0.5

1.0

1.5

2.0

2.5

0.0

-120

-100

-80

-60

-40

-20

0

0.5

1.0

1.5

2.0

2.5

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V58C2256804SHUD6E | 32M X 8 DDR DRAM, PDSO66 |

| V58C2256804SHUI4 | 32M X 8 DDR DRAM, PDSO66 |

| V59C1512164QCF3I | 32M X 16 DDR DRAM, 0.45 ns, PBGA84 |

| V59C1G01168QBLJ-25I | DDR DRAM, PBGA84 |

| V59C1G01408QAUP25A | 256M X 4 DDR DRAM, PBGA68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V58C265164S | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:64 Mbit DDR SDRAM 2.5 VOLT 4M X 16 |

| V58C265404S | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 16M X 4 DDR SDRAM 4 BANKS X 4Mbit X 4 |

| V58C265804S | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 8M X 8 DDR SDRAM 4 BANKS X 2Mbit X 8 |

| V58C3643204SAT | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:HIGH PERFORMANCE 3.3 VOLT 2M X 32 DDR SDRAM 4 X 512K X 32 |

| V58C365164S | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:64 Mbit DDR SDRAM 4M X 16, 3.3VOLT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。