- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361594 > UPSD33XX (意法半導(dǎo)體) Fast 8032 MCU with Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | UPSD33XX |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Fast 8032 MCU with Programmable Logic |

| 中文描述: | 8032微控制器的快速可編程邏輯 |

| 文件頁數(shù): | 179/231頁 |

| 文件大?。?/td> | 1805K |

| 代理商: | UPSD33XX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁當(dāng)前第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁

179/231

uPSD33xx

JTAG ISP Mode.

Four of the pins on Port C are

based on the IEEE 1149.1 JTAG specification and

are used for In-System Programming (ISP) of the

PSD Module and debugging of the 8032 MCU

Module. These pins (TDI, TDO, TMS, TCK) are

dedicated to JTAG and cannot be used for any

other I/O function. There are two optional pins on

Port C (TSTAT and TERR) that can be used to re-

duce programming time during ISP. See

JTAG

ISP and JTAG Debug, page 195

.

Other Port Capabilities.

It is possible to change

the type of output drive on the ports at run-time. It

is also possible to read the state of the output en-

able signal of the output driver at run-time. The fol-

lowing sections provide the details.

Port Pin Drive Options.

The csiop Drive Select

registers allow reconfiguration of the output drive

type for certain pins on Ports A, B, C, and D. The

8032 can change the default drive type setting at

run-time. The is no action needed in PSDsoft Ex-

press to change or define these pin output drive

types.

Figure 69., page 169

shows the csiop Drive

Select register output controlling the pin output

driver. The default setting for drive type for all pins

on Ports A, B, C, and D is a standard CMOS push-

pull output driver.

Note:

When a pin on Port A, B, C, D is not used as

an output and has no external device driving it as

an input (floating pin), excess power consumption

can be avoided by placing a weak pull-up resistor

(100K

) to V

DD

which keeps the CMOS input pin

from floating.

Drive Select Registers.

The csiop Drive Select

Registers will configure a pin output driver as

Open Drain or CMOS push/pull for some port pins,

and controls the slew rate for other port pins. An

external pull-up resistor should be used for pins

configured as Open Drain, and the resistor should

be sized not to exceed the current sink capability

of the pin (see DC specifications). Open Drain out-

puts are diode clamped, thus the maximum volt-

age on an pin configured as Open Drain is V

DD

+

0.7V.

A pin can be configured as Open Drain if its corre-

sponding bit in the Drive Select Register is set to

logic '1.'

Note:

The slew rate is a measurement of the rise

and fall times of an output. A higher slew rate

means a faster output response and may create

more electrical noise. A pin operates in a high slew

rate when the corresponding bit in the Drive Reg-

ister is set to '1.' The default rate is standard slew

rate (see AC specifications).

Table

109

through

Table 112., page 180

show the

csiop Drive Registers for Ports A, B, C, and D. The

tables summarize which pins can be configured as

Open Drain outputs and which pins the slew rate

can be changed. The default output type is CMOS

push/pull output with normal slew rate.

Enable Out Registers.

The state of the output

enable signal for the output driver at each pin on

Ports A, B, C, and D can be read at any time by the

8032 when it reads the csiop Enable Output regis-

ters. Logic '1' means the driver is in output mode,

logic ’0’ means the output driver is in high-imped-

ance mode, making the pin suitable for input mode

(read by the input buffer shown in

Figure

69., page 169

). Figure

69

shows the three sources

that can control the pin output enable signal: a

product term from AND-OR array; the csiop Direc-

tion register; or the Peripheral I/O Mode logic (Port

A only). The csiop Enable Out registers represent

the state of the final output enable signal for each

port pin driver, and are defined in

Table

113., page 180

through

Table 116., page 180

.

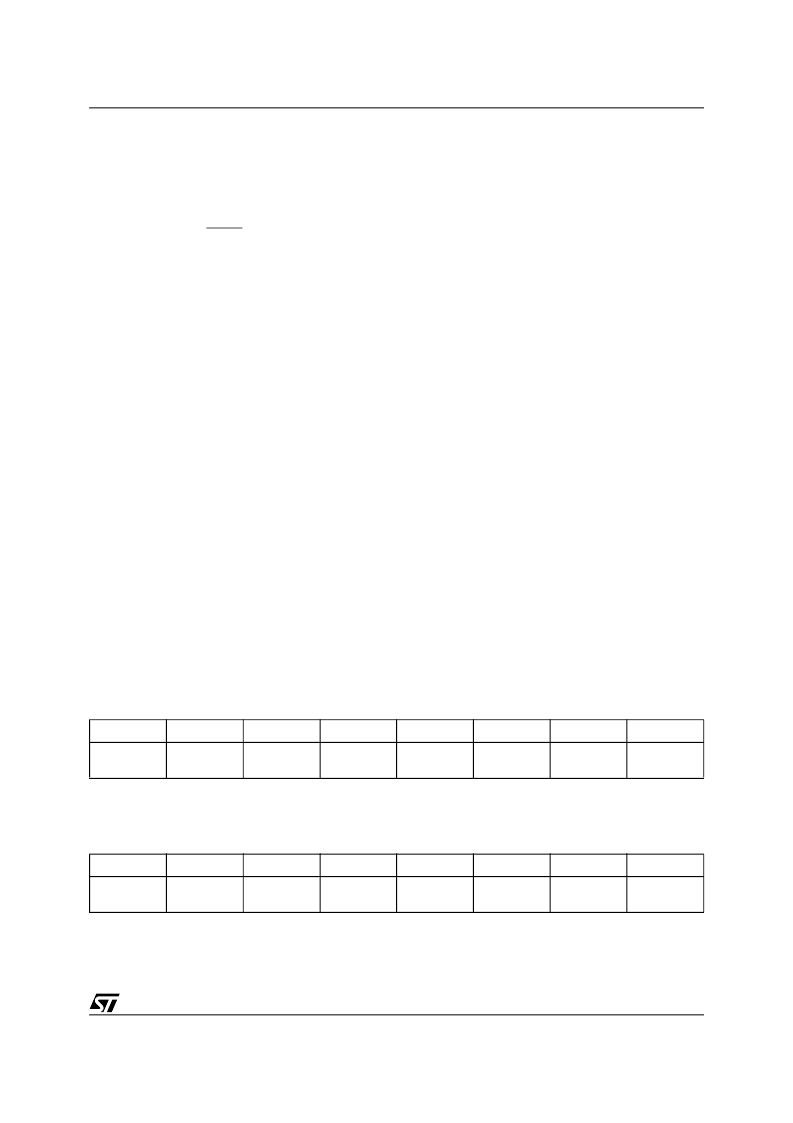

Table 109. Port A Pin Drive Select Register

(1)

(address = csiop + offset 08h)

Note: 1. Port A not available on 52-pin uPSD33xx devices

2. For each bit, 1 = pin drive type is selected, 0 = pin drive type is default mode, CMOS push/pull

3. Default state for register is 00h after reset or power-up

Table 110. Port B Pin Drive Select Register (address = csiop + offset 09h)

Note: 1. For each bit, 1 = pin drive type is selected, 0 = pin drive type is default mode, CMOS push/pull

2. Default state for register is 00h after reset or power-up

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

PA7

Open Drain

PA6

Open Drain

PA5

Open Drain

PA4

Open Drain

PA3

Slew Rate

PA2

Slew Rate

PA1

Slew Rate

PA0

Slew Rate

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

PB7

Open Drain

PB6

Open Drain

PB5

Open Drain

PB4

Open Drain

PB3

Slew Rate

PB2

Slew Rate

PB1

Slew Rate

PB0

Slew Rate

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| uPSD3412C-24U6T | Flash Programmable System Devices with 8032 Microcontroller Core and 16Kbit SRAM |

| UPSD3422EV | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic(帶有USB和可編程邏輯的Turbo Plus系列快速Turbo 8032 MCU) |

| UPSD3434EV | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic(帶有USB和可編程邏輯的Turbo Plus系列快速Turbo 8032 MCU) |

| UPSD3432 | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

| UPSD3432E | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPSD3422E-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422E-40U6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40T6 | 功能描述:8位微控制器 -MCU Turbo 8032 MCU w/USB & Programmable Logic RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40U6 | 功能描述:8位微控制器 -MCU uPSD34x Turbo Plus Fast Turbo 8032 MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EV-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。