- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄361594 > UPSD33XX (意法半導(dǎo)體) Fast 8032 MCU with Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | UPSD33XX |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Fast 8032 MCU with Programmable Logic |

| 中文描述: | 8032微控制器的快速可編程邏輯 |

| 文件頁(yè)數(shù): | 135/231頁(yè) |

| 文件大小: | 1805K |

| 代理商: | UPSD33XX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)當(dāng)前第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)

135/231

uPSD33xx

Table 75. uPSD33xx Memory Configuration

Runtime Control Registers, CSIOP.

A block of

256 bytes is decoded inside the PSD Module for

module

control

and

79., page 145

). The base address of these 256 lo-

cations is referred to in this data sheet as csiop

(Chip Select I/O Port), and is selected by the De-

code PLD output signal, CSIOP. The csiop regis-

ters are always viewed by the 8032 as XDATA,

and are accessed with RD and WR signals. The

address range of CSIOP is specified using PSD-

soft Express where the user only has to specify an

address range of 256 bytes, and then the RD or

WR signals are automatically activated for the

specified range. Individual registers within this

block are accessed with an offset from the speci-

fied csiop base address. 39 registers are used out

of the 256 locations to control the output state of I/

O pins, to read I/O pins, to set the memory page,

to control 8032 program and data address space,

to control power management, to READ/WRITE

macrocells inside the General PLD, and other

functions during runtime. Unused locations within

csiop are reserved and should not be accessed.

Memory Page Register.

8032 MCU architecture

has an inherent size limit of 64K bytes in either

program address space or XDATA space. Some

uPSD33xx devices have much more memory that

64K, so special logic such as this page register is

needed to access the extra memory. This 8-bit

page register (Figure

52

) can be loaded and read

by the 8032 at runtime as one of the csiop regis-

ters. Page register outputs feed directly into both

PLDs creating extended address signals used to

“page” memory beyond the 64K byte limit (pro-

gram space or XDATA). Most 8051 compilers di-

rectly support memory paging, also known as

memory banking. If memory paging is not needed,

or if not all eight page register bits are needed for

memory paging, the remaining bits may be used in

the General PLD for general logic. Page Register

outputs are cleared to logic ’0’ at reset and power-

up.

status

(see

Table

Programmable Logic (PLDs) .

The uPSD33xx

contains two PLDs (

Figure 63., page 157

) that

may optionally run in Turbo or Non-Turbo mode.

PLDs operate faster (less propagation delay)

while in Turbo mode but consume more power

than in Non-Turbo mode. Non-Turbo mode allows

the PLDs to go to standby automatically when no

PLD inputs are changing to conserve power.

The logic configuration (from equations) of both

PLDs is stored with non-volatile Flash technology

and the logic is active upon power-up. PLDs may

NOT be programmed by the 8032, PLD program-

ming only occurs through the JTAG interface.

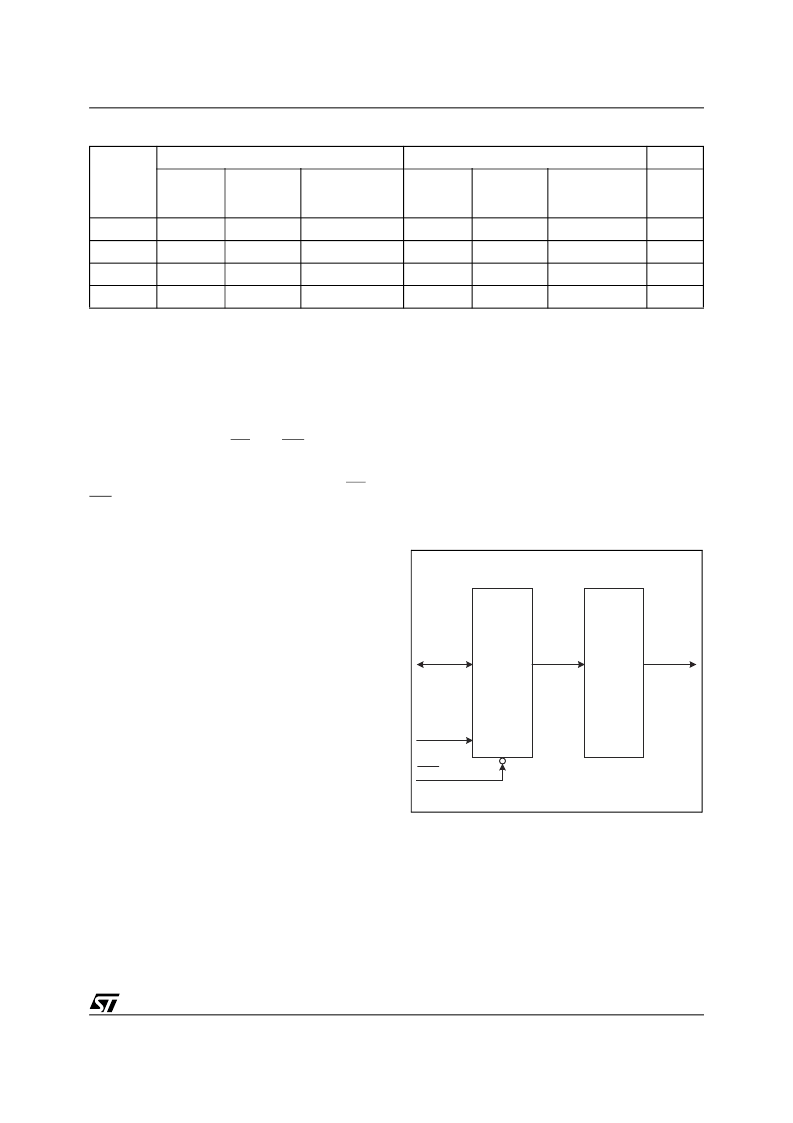

Figure 52. Memory Page Register

Device

Main Flash Memory

Secondary Flash Memory

SRAM

Total

Flash Size

(bytes)

Individual

Sector Size

(bytes)

Number of

Sectors (Sector

Select Signal)

Total

Flash Size

(bytes)

Individual

Sector Size

(bytes)

Number of

Sectors (Sector

Select Signal)

SRAM

Size

(bytes)

uPSD3312

64K

16K

4 (FS0-3)

16K

8K

2 (CSBOOT0-1)

2K

uPSD3333

128K

16K

8 (FS0-7)

32K

8K

4 (CSBOOT0-3)

8K

uPSD3334

256K

32K

8 (FS0-7)

32K

8K

4 (CSBOOT0-3)

8K

uPSD3354

256K

32K

8 (FS0-7)

32K

8K

4 (CSBOOT0-3)

32K

8032

Data

Bus

Load or

Read via

csiop +

offset E0h

D0

D7

D6

D5

D4

D3

D2

D1

Q0

Q1

Q7

Q6

Q5

Q4

Q3

Q2

DPLD

and

GPLD

Page

Register

Chip-

Selects

and

General

Logic

RST

(PSD Module Reset)

RST

PGR0-7

AI09172

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| uPSD3412C-24U6T | Flash Programmable System Devices with 8032 Microcontroller Core and 16Kbit SRAM |

| UPSD3422EV | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic(帶有USB和可編程邏輯的Turbo Plus系列快速Turbo 8032 MCU) |

| UPSD3434EV | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic(帶有USB和可編程邏輯的Turbo Plus系列快速Turbo 8032 MCU) |

| UPSD3432 | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

| UPSD3432E | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPSD3422E-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422E-40U6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40T6 | 功能描述:8位微控制器 -MCU Turbo 8032 MCU w/USB & Programmable Logic RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40U6 | 功能描述:8位微控制器 -MCU uPSD34x Turbo Plus Fast Turbo 8032 MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EV-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。