- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379494 > UPD17228MC (NEC Corp.) 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER PDF資料下載

參數(shù)資料

| 型號(hào): | UPD17228MC |

| 廠商: | NEC Corp. |

| 元件分類: | 4位微控制器 |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER |

| 中文描述: | 4位單片機(jī)的小型通用紅外遙控器 |

| 文件頁(yè)數(shù): | 17/84頁(yè) |

| 文件大小: | 393K |

| 代理商: | UPD17228MC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

μ

PD17225, 17226, 17227, 17228

17

Data Sheet U12643EJ2V0DS00

2.4.2

System registers (SYSREG)

The system registers are registers that are directly related to control of the CPU. These registers are mapped to

addresses 74H-7FH on the data memory and can be referenced regardless of bank specification.

The system registers include the following registers:

Address registers (AR0-AR3)

Note

Window register (WR)

Bank register (BANK)

Note

Memory pointer enable flag (MPE)

Memory pointers (MPH, MPL)

Index registers (IXH, IXM, IXL)

General register pointers (RPH, RPL)

Program status word (PSWORD)

Note

The address register (AR3) and the bank register (BANK) are fixed to 0 in the

μ

PD17225 and 17226.

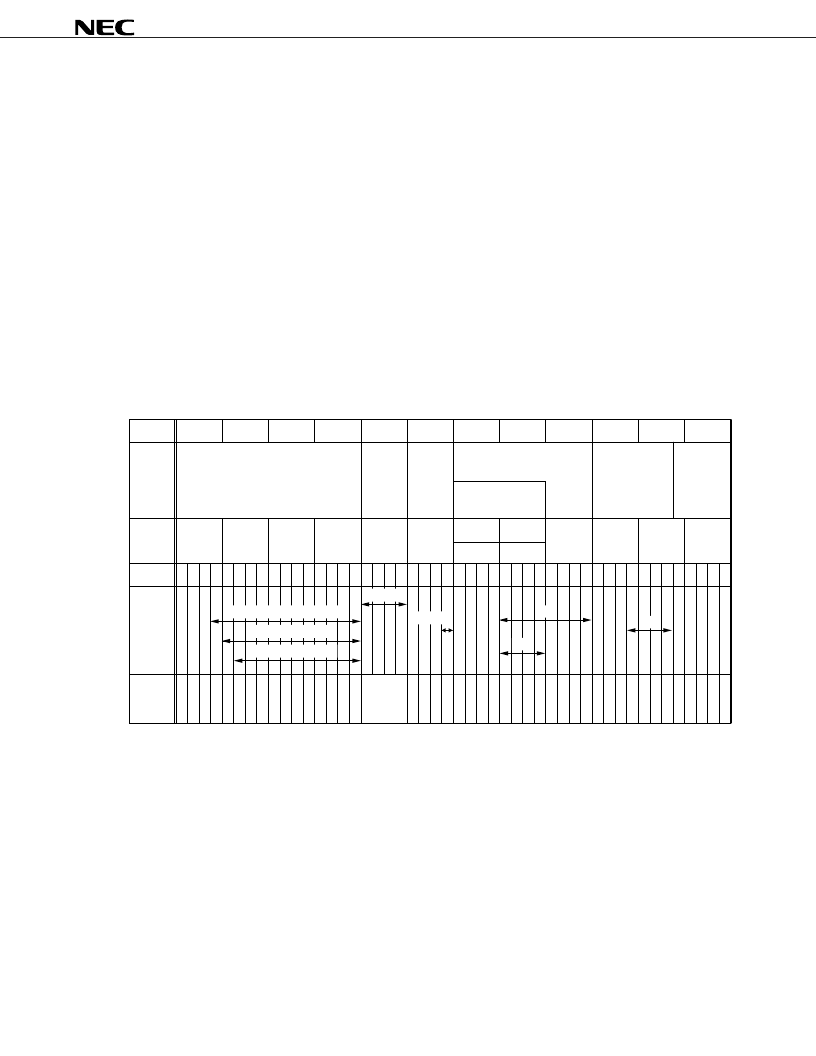

Figure 2-5. Configuration of System Register

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

74H

75H

76H

77H

78H

79H

7AH

7BH

7CH

7DH

7EH

7FH

AR 3

AR 2

AR 1

AR 0

WR

BANK

IXH

IXM

IXL

RPH

RPL

PSW

MPH

MPL

Address register

(AR)

Window

register

(WR)

Bank

register

(BANK)

Data memory

row address

pointer (MP)

Index register

(IX)

General

register

pointer

(RP)

Program

status

word

(PSWORD)

0 0 0

0 0

0 0

0 0

M

P

E

B

C

D

C

M

P

C

Y Z

I

X

E

(RP)

(IX)

(MP)

(BANK)

Data

Bit

Symbol

Name

Address

Initial

Value

At

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Undefined

0

0

0

(WR)

*

*

*

*

(AR) ( PD17227, 17228)

(AR) ( PD17226)

(AR) ( PD17225)

μ

0 0 0 0 0

0 0 0 0

Note

*: This bit is fixed to 0 in the

μ

PD17225 and 17226.

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。