- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382720 > UDA1325 (NXP Semiconductors N.V.) Universal Serial Bus USB CODEC PDF資料下載

參數(shù)資料

| 型號(hào): | UDA1325 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | Codec |

| 英文描述: | Universal Serial Bus USB CODEC |

| 中文描述: | 通用串行總線解碼器 |

| 文件頁數(shù): | 35/52頁 |

| 文件大小: | 310K |

| 代理商: | UDA1325 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

1999 May 10

35

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) CODEC

UDA1325

V

ALIDATE BUFFER

Command: FAh.

Data: none.

When the microcontroller has written data into an IN buffer,

it should set the buffer full flag by the validate buffer

command. This indicates that the data in the buffer are

valid and can be sent to the host when the next IN token is

received.

General commands

R

EAD CURRENT FRAME NUMBER

Command: F5h.

Data: read 1 or 2 bytes.

This command is followed by one or two data reads and

returns the frame number of the last successfully received

SOF. The frame number is eleven bits wide. The frame

number is returned least significant byte first. In case the

user is only interested in the lower 8 bits of the frame

number only the first byte needs to be read.

I

2

C MASTER/SLAVE INTERFACE

The I

2

C module implements a master/slave I

2

C-bus

interface with integrated shift register, shift timing

generation and slave address recognition. It is compliant

to the I

2

C-bus specification IC20/Jan92. I

2

C standard

mode (100 kHz SCL) and fast mode (400 kHz) are

supported. Low speed mode and extended 10 bit

addressing are unsupported.

Characteristics of the I

2

C-bus

The I

2

C-bus is for 2-way, 2-line communication between

different ICs or modules. The two lines are a serial data

line (SDA) and a Serial Clock Line (SCL). Both lines must

be connected to V

DDE

via a pull-up resistor.

The timing definition of the I

2

C-bus is given in Fig.7.

Programmer’s view

For a detailed description of the I

2

C-bus protocol refer to

Philips Integrated Circuits Data Handbook IC20, 8XC552.

The programmer’s view of the I

2

C library function is -with

one exception- identical to that of the 8XC552

microcontroller. Only the bit rate frequency selection in

S1CON and the handling of the Timer 1 overflow

information deviates to accommodate 400 kHz operation.

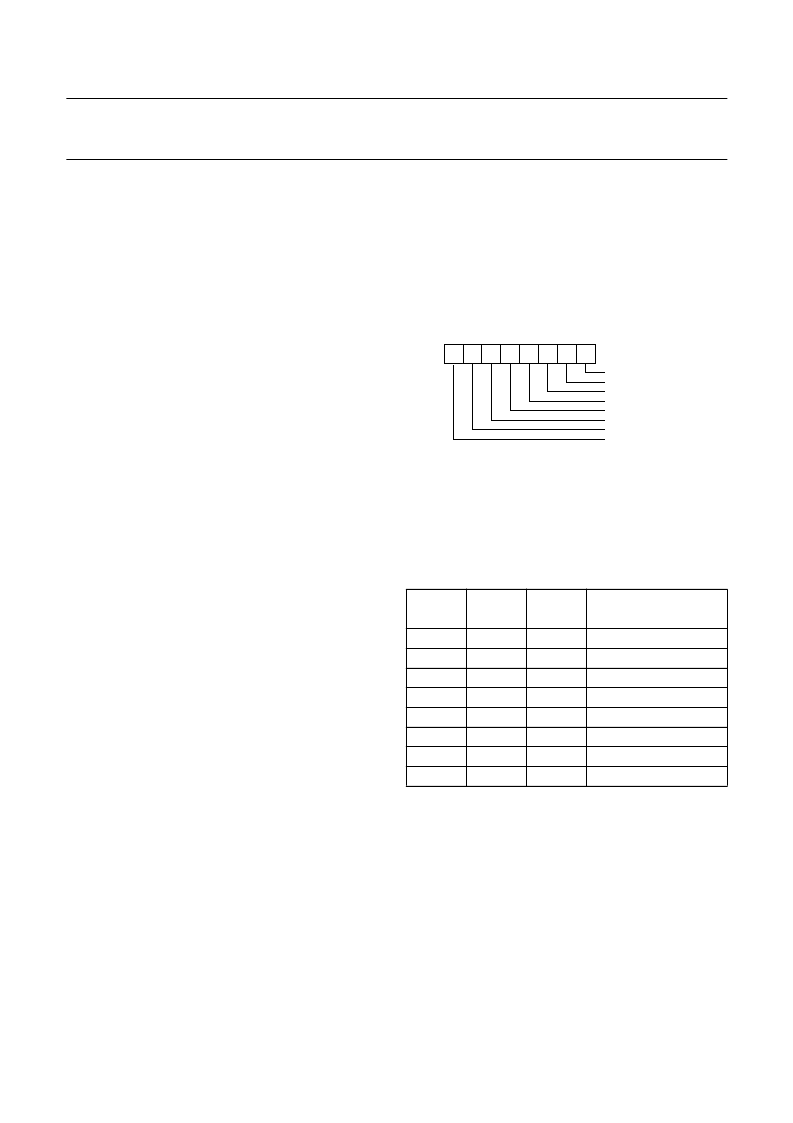

S1CON register

The CPU can read from and write to this 8-bit SFR.

Two bits are effected by the SIO1 hardware: the SI bit is

set when a serial interrupt is requested, and the STO bit is

cleared when a STOP condition is present on the I

2

C-bus.

The STO bit is also cleared when ENS1 = ‘0’. Reset

initializes S1CON to 00h.

CR2, 1

AND

0 -

THE CLOCK RATE BITS

These three bits determine the serial clock frequency

when SIO1 is in a master mode.

The various serial rates are shown in Table 28.

Table 28

Serial clock rates (SCL line)

When the CR bits are ‘111’, the maximum bit rate for the

data transfer will be derived from the Timer 1 overflow rate

divided by 2 (i.e. every time the Timer 1 overflows, the

SCL signal will toggle).

CR2

CR1

CR0

I

2

C BIT FREQUENCY

(kHz)

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1200

600

400

300

150

100

75

3.9 ... 501

0

0

0

0

0

0

0

0

CR0

CR1

AA

SI

STO

STA

ENS1

CR2

7

6

5

4

3

2

1

0

Power On Value

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UDA1325H | Universal Serial Bus USB CODEC |

| UDA1325PS | Universal Serial Bus USB CODEC |

| UDA1326PS | USB AUDIO-CODEC(通用串行總線音頻編解碼器) |

| UDA1331H | Universal Serial Bus USB Audio Playback Peripheral APP |

| UDA1334BT | Low power audio DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UDA1325H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Universal Serial Bus USB CODEC |

| UDA1325PS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Universal Serial Bus USB CODEC |

| UDA1328 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi-channel filter DAC |

| UDA1328T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi-channel filter DAC |

| UDA1330A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low-cost stereo filter DAC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。