- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371188 > TSA5059 (NXP Semiconductors N.V.) 2.7 GHz I2C-bus controlled low phase noise frequency synthesizer PDF資料下載

參數(shù)資料

| 型號: | TSA5059 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 2.7 GHz I2C-bus controlled low phase noise frequency synthesizer |

| 中文描述: | 2.7千兆赫的I2C控制的低相位噪聲頻率合成器總線 |

| 文件頁數(shù): | 6/24頁 |

| 文件大小: | 151K |

| 代理商: | TSA5059 |

1999 Oct 05

6

Philips Semiconductors

Preliminary specification

2.7 GHz I

2

C-bus controlled low phase

noise frequency synthesizer

TSA5059

Four open-collector output ports are provided on the IC for

general purpose; three of these can also be used as input

ports. A 3-bit ADC is also available.

The TSA5059 is controlled via the two-wire I

2

C-bus.

For programming, there is one 7-bit module address and

the R/W bit for selecting READ or WRITE mode. To be

able to have more than one synthesizer in an I

2

C-bus

system, one of four possible addresses is selected

depending on the voltage applied at pin AS (see Table 3).

The TSA5059 fulfils the fast mode I

2

C-bus, according to

the Philips I

2

C-bus specification. The I

2

C-bus interface is

designed in such a way that pins SCL and SDA can be

connected either to 5 or to 3.3 V pulled-up I

2

C-bus lines,

allowing the PLL synthesizer to be connected directly to

the bus lines of a 3.3 V microcontroller.

WRITE mode: R/W = 0

After the address transmission (first byte), data bytes can

be sent to the device (see Table 1). Four data bytes are

neededtofullyprogramtheTSA5059.Thebustransceiver

has an auto-increment facility that permits programming of

the TSA5059 within one single transmission

(address + 4 data bytes).

The TSA5059 can also be partly programmed on the

condition that the first data byte following the address is

byte 2 or byte 4. The meaning of the bits in the data bytes

is given in Table 1. The first bit of the first data byte

transmitted indicates whether byte 2 (first bit is logic 0) or

byte 4 (first bit is logic 1) will follow. Until an I

2

C-bus STOP

condition is sent by the controller, additional data bytes

can be entered without the need to re-address the device.

To allow a smooth frequency sweep for fine tuning, and

while the data of the dividing ratio of the main divider is in

data bytes 2, 3 and 4, it is necessary for changing the

frequency to send the data bytes 2 to 5 in a repeated

sending, or to finish an incomplete transmission by a

STOP condition. Repeated sending of data bytes 2 and 3

without ending the transmission does not change the

dividing ratio. To illustrate, the following data sequences

will change the dividing ratio:

Bytes 2, 3, 4 and 5

Bytes 4, 5, 2 and 3

Bytes 2, 3, 4 and STOP

Bytes 4, 5, 2 and STOP

Bytes 2, 3 and STOP

Bytes 2 and STOP

Bytes 4 and STOP.

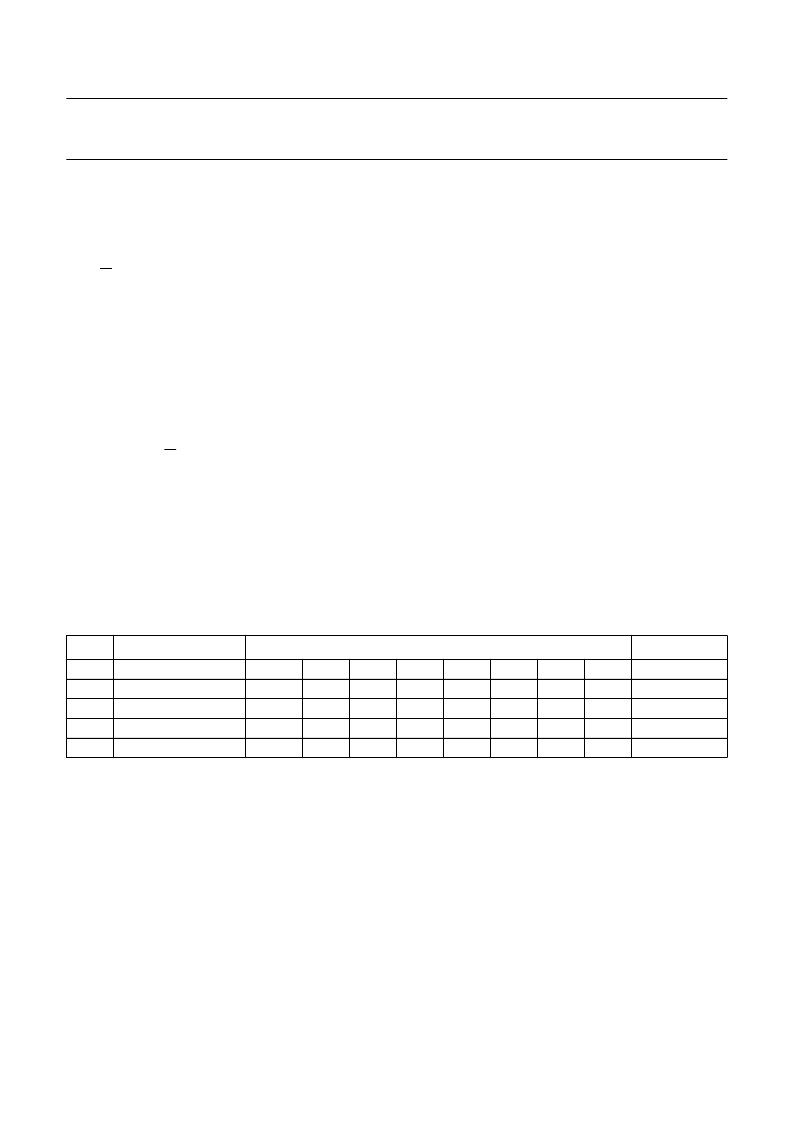

Table 1

Write data format

Note

1.

MSB is transmitted first.

BYTE

DESCRIPTION

MSB

(1)

LSB

CONTROL BIT

1

2

3

4

5

address

programmable divider

programmable divider

control data

control data

1

0

1

0

0

0

MA1

N10

N2

R2

P2/T2

MA0

N9

N1

R1

P1/T1

0

A

A

A

A

A

N14

N6

N16

C0

N13

N5

N15

XCE

N12

N4

PE

XCS

N11

N3

R3

P3

N8

N0

R0

N7

1

C1

P0/T0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSA5059T | 2.7 GHz I2C-bus controlled low phase noise frequency synthesizer |

| TSC2200 | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IPW | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IPWR | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IRHB | PDA ANALOG INTERFACE CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSA5059A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.7 GHz I2C-bus controlled low phase noise frequency synthesizer |

| TSA5059AT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.7 GHz I2C-bus controlled low phase noise frequency synthesizer |

| TSA5059AT/C2,518 | 制造商:NXP Semiconductors 功能描述: |

| TSA5059ATS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.7 GHz I2C-bus controlled low phase noise frequency synthesizer |

| TSA5059ATS/C1,118 | 功能描述:鎖相環(huán) - PLL 2,7GHZI2C BUS RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。