- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373715 > TS68EN360VR25L (ATMEL CORP) 32-bit Quad Integrated Communication Controller PDF資料下載

參數(shù)資料

| 型號: | TS68EN360VR25L |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-bit Quad Integrated Communication Controller |

| 中文描述: | 32-BIT, 25 MHz, RISC PROCESSOR, CPGA241 |

| 封裝: | CERAMIC, PGA-241 |

| 文件頁數(shù): | 74/82頁 |

| 文件大?。?/td> | 874K |

| 代理商: | TS68EN360VR25L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當前第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

74

TS68EN360

2113A–HIREL–03/02

TheCPprovidesthecommunicationfeaturesoftheQUICC.IncludedareaRISCpro-

cessor,fourSCCs,twoSMCs,oneSPI,2.5Kbytesofdual-portRAM,aninterrupt

controller,atimeslotassigner,threeparallelports,aparallelinterfaceport,fourinde-

pendentbaudrategenerators,andfourteenserialDMAchannelstosupporttheSCCs,

SMCs,andSPI.

TheIDMAsprovidetwochannelsofgeneral-purposeDMAcapability.Theyofferhigh-

speedtransfers,32-bitdatamovement,bufferchaining,andindependentrequestand

acknowledgelogic.TheRISCcontrollermayaccesstheIDMAregistersdirectlyinthe

bufferchainingmodes.TheQUICCIDMAsaresimilarto,yetenhancementsof,theone

IDMAchannelfoundontheTS68302.

Thefourgeneral-purposetimersontheQUICCarefunctionallysimilartothetwogen-

eral-purposetimersfoundontheTS68302.However,theyoffersomeminor

enhancements,suchastheinternalcascadingoftwotimerstoforma32-bittimer.The

QUICCalsocontainsaperiodicintervaltimerintheSIM60,bringingthetotaltofive

on-chiptimers.

EthernetonQUICC

TheEthernetprotocolisavailableonlyontheEthernetversionoftheQUICCcalledthe

TS68EN360.Thenon-EthernetversionoftheQUICCistheMC68360.Theterm

“QUICC”istheoveralldevicenamethatdenotesallversionsofthedevice.

TheTS68EN360isasupersetoftheMC68360,havingtheadditionaloptionallowing

EthernetoperationonanyofthefourSCCs.DuetoperformancereasonnotassSCCs

canbeconfiguredasEthernetcontrolleratthesametime.TheTS68EN360isnot

restrictedonlytoEthernetoperation.HDLC,UART,andotherprotocolsmaybeusedto

allowdynamicswitchingbetweenprotocols.SeeAppendixASerialPerformancefor

availableSCCperformance.

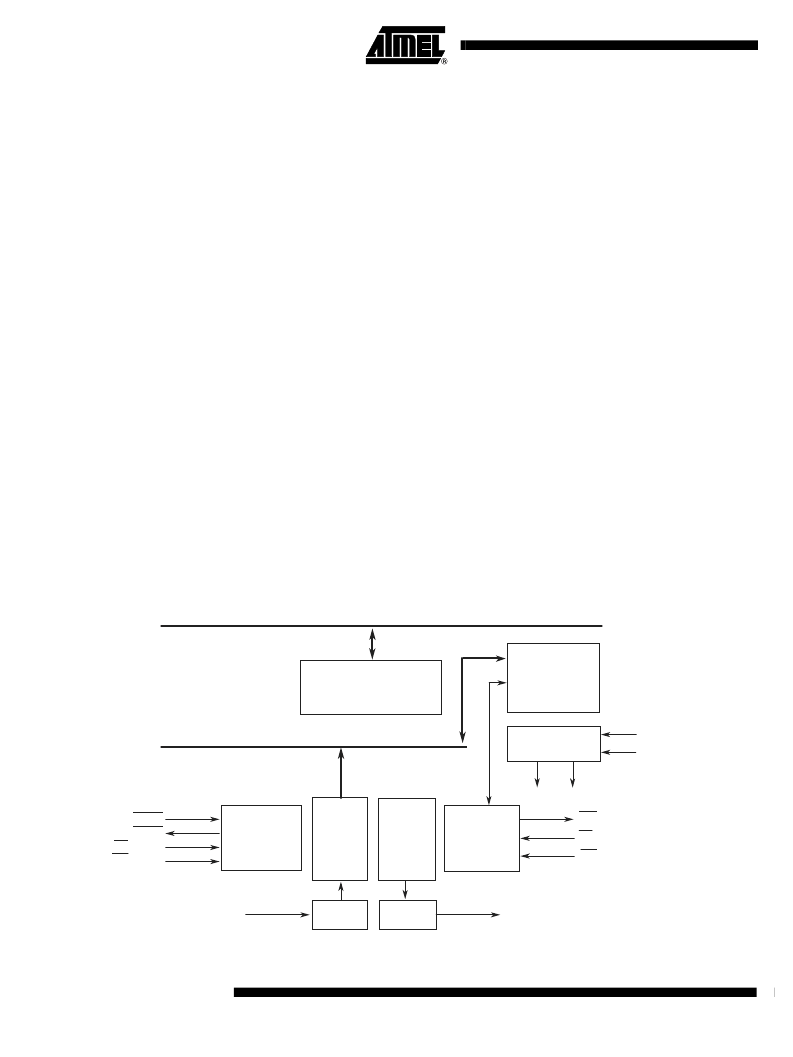

WhentheMODEbitsoftheSCCGSMRselecttheEthernetprotocol,thenthatSCC

performsthefullsetofIEEE802.3/EthernetCSMA/CDmediaaccesscontrolandchan-

nelinterfacefunctions(seeFigure73).

Figure73.

EthernetBlockDiagram

IMB

CONTROL

REGISTERS

SLOT TIME

AND DEFER

COUNTER

CLOCK

GENERATOR

PERIPHERAL BUS

RECEIVER

CONTROL

UNIT

RECEIVE

DATA

FIFO

TRANSMITTER

CONTROL

UNIT

TRANSMIT

DATA

FIFO

SHIFTER

SHIFTER

TXD

RXD

RRJCT

RSTRT

CD = RENA

CTS = CLSN

CD = RENA

CTS = CLSN

RTS = TENA

INTERNAL CLOCKS

RX CLOCK

TX CLOCK

R

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68EN360VR33L | 32-bit Quad Integrated Communication Controller |

| TS68EN360DES01MXCL | 32-bit Quad Integrated Communication Controller |

| TS68EN360 | 32-bit Quad Integrated Communication Controller |

| TS68EN360DES02MXCL | 32-bit Quad Integrated Communication Controller |

| TS68EN360MA25L | 32-bit Quad Integrated Communication Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68EN360VR33L | 制造商:e2v technologies 功能描述:TS68EN360VR33L - Trays |

| TS68HC811E2MC1B/C | 制造商:e2v technologies 功能描述:TS68HC811E2MC1B/C - Rail/Tube |

| TS68HC901 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HCMOS MULTI-FUNCTION PERIPHERAL |

| TS68HC901CFN4 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HCMOS MULTI-FUNCTION PERIPHERAL |

| TS68HC901CFN5 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HCMOS MULTI-FUNCTION PERIPHERAL |

發(fā)布緊急采購,3分鐘左右您將得到回復。