- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373715 > TS68C429ADESCxx (Atmel Corp.) CMOS ARINC 429 Multichannel Receiver/ Transmitter MRT PDF資料下載

參數(shù)資料

| 型號: | TS68C429ADESCxx |

| 廠商: | Atmel Corp. |

| 英文描述: | CMOS ARINC 429 Multichannel Receiver/ Transmitter MRT |

| 中文描述: | ARINC公司429多通道的CMOS接收器/發(fā)送捷運 |

| 文件頁數(shù): | 21/43頁 |

| 文件大?。?/td> | 1638K |

| 代理商: | TS68C429ADESCXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

21

TS68C429A

2120A–HIREL–08/02

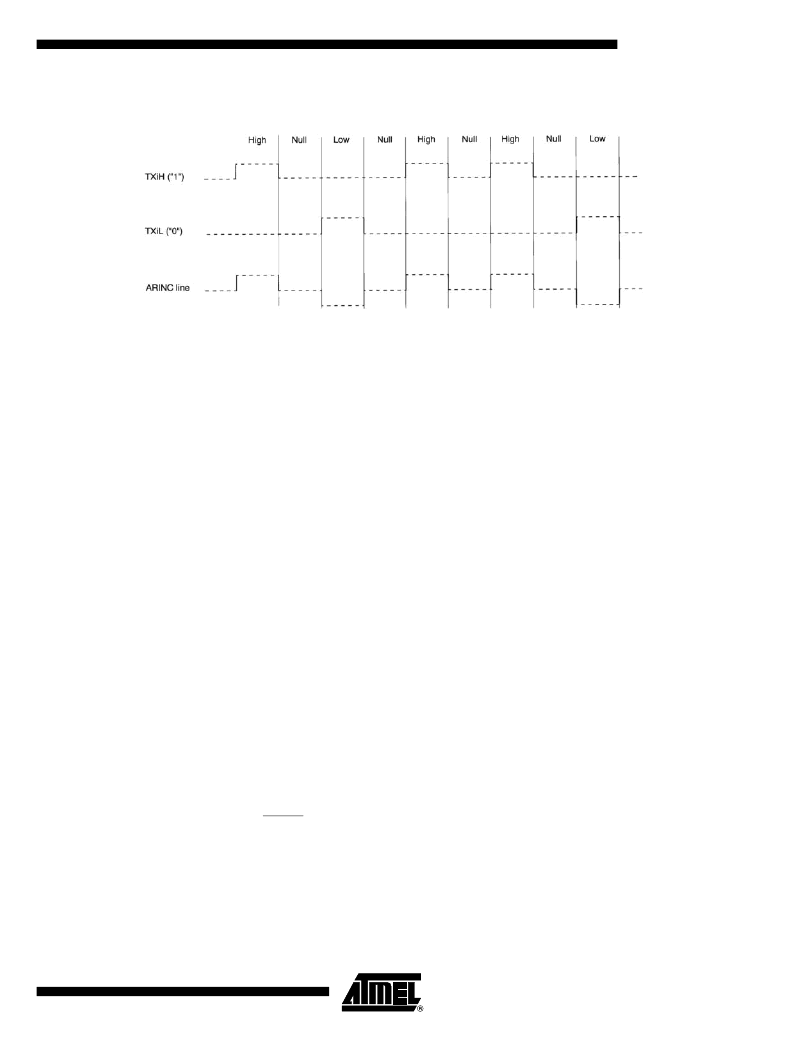

Figure 15.

Transmitter Channel Unit Outputs

Description

The block diagram of a transmit channel is given is given in Figure 16. Only the third

channel can be switched to internal lines for test mode, otherwise the channels are iden-

tical. The selection of this test mode is done by programming the test bit in the

transmitter-control-register (see “Register Description” on page 17). In this test mode

the lines TX3H and TX3L are not driven, they are both kept at “0”.

The transmit frequency is generated by dividing the ARINC clock signal (CLK ARINC)

by the value contained in the frequency register. This divided clock synchronizes the

shift register which sends the 32-bit word on the lines TXiH and TXiL.

The parity is computed and if requested (see “Register Description” on page 17) the par-

ity bit (32nd bit of the message) is modified to have an odd number of “1” in the 32-bit

message for odd parity or an even number of “1” in the 32-bit message for even parity.

A gap control block generates a gap between the sent messages. The value of this gap

is defined by the 5 bits “transmission gap” of the transmitter-control-register, it is given in

number of ARINC bit (see “Register Description” on page 17).

A FIFO control block manages the messages to be sent. Up to 8 messages can be writ-

ten into the FIFO. The FIFO is seen as a two 16-bit memory words, the Most Significant

Word of the message (MSW) is written in the lower address, the Least Significant Word

of the message (LSW) is written in the upper address. The MSW should be written first.

The access to the FIFO is 16 bits mandatory. The number of messages within the FIFO

is indicated by a counter that can be read through the transmitter-control-register. This

counter is incremented when the LSW is written and decremented when the message is

transferred to the shift-register. The “Reset FIFO” bit is used to cancel messages within

the FIFO. If a transmission is on going, the entire message will be sent. The “reset

FIFO” bit remains active until written at 1 by the microprocessor. When the transmitter is

disable during a transmission, the out going message is lost.

When the FIFO is empty, a bit is set in the status-register (see “General Circuit Control”

on page 24). If the interrupt mode is enabled (see “General Circuit Control” on page 24)

the IRQTX line is activated.

When the transmitter FIFO is empty and when no transmission is on going, the first write

access to the FIFO has to be preceded by the following sequence: disable and enable

transmission (see Figure 36: First FIFO access).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68EN360VR25L | 32-bit Quad Integrated Communication Controller |

| TS68EN360VR33L | 32-bit Quad Integrated Communication Controller |

| TS68EN360DES01MXCL | 32-bit Quad Integrated Communication Controller |

| TS68EN360 | 32-bit Quad Integrated Communication Controller |

| TS68EN360DES02MXCL | 32-bit Quad Integrated Communication Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68C429AMF | 功能描述:IC MULTI-CH CTRLR 132CQFP RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TS68C429AMF1B/C | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:CMOS ARINC 429 Multichannel Receiver/ Transmitter MRT |

| TS68C429AMF1BC | 制造商:e2v technologies 功能描述:TS68C429AMF1BC - Trays |

| TS68C429AMF1BCA | 制造商:e2v technologies 功能描述:TS68C429AMF1BCA - Trays |

| TS68C429AMFA | 制造商:e2v technologies 功能描述:MULTI CH RCVR/TRANSMITTER 132CQFP - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。