- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382685 > TRU2500-C Telecomm/Datacomm PDF資料下載

參數(shù)資料

| 型號(hào): | TRU2500-C |

| 元件分類: | 通信、網(wǎng)絡(luò)模塊及開(kāi)發(fā)工具 |

| 英文描述: | Telecomm/Datacomm |

| 中文描述: | 電信/數(shù)據(jù)通信 |

| 文件頁(yè)數(shù): | 2/12頁(yè) |

| 文件大?。?/td> | 825K |

| 代理商: | TRU2500-C |

Vectron International 166 Glover Avenue, Norwalk, CT 06856 Tel: 1-88-VECTRON-1 Fax: 1-888-FAX-VECTRON

The TRU2500 combines Vectron s SAW filter exper-

tise with custom GaAs ASIC technology for high per-

formance timing recovery applications. The circuit is

assembled on a precision ceramic hybrid and pack-

aged in a hermetic SMD package with industry com-

mon footprint and pinout. Precision SAW filter technol-

ogy assures full Bellcore compliance over all operating

conditions and eliminates the need for external tuning

or compensation.

High bit-rate SAW filter clock recovery was developed

for and has been proven in high reliability undersea links.

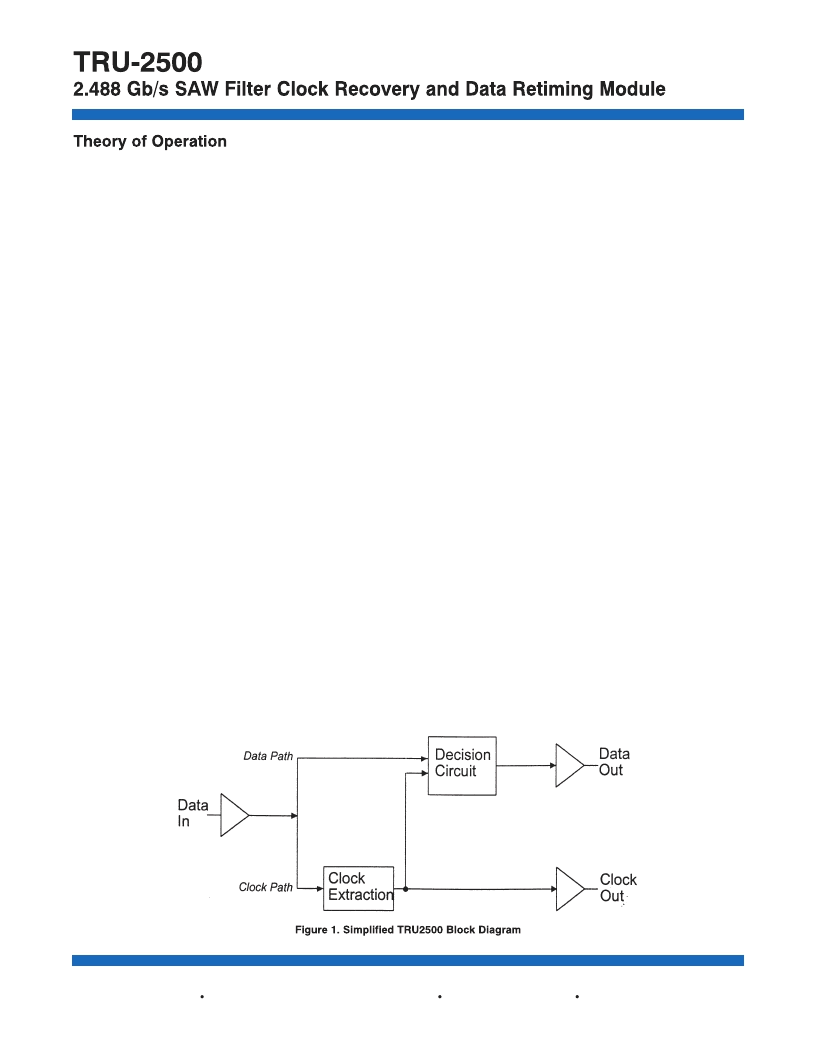

The timing recovery circuit must extract a clean clock

signal from an input NRZ data stream and then reclock

the data with the clock. A simplified block diagram of a

basic timing recovery circuit is shown in Fig 1.The data

retiming aspect of the design is somewhat straightfor-

ward. Recovering a clock compliant with jitter standards

and maintaining acceptable clock to data alignment at

the decision circuit are the most difficult aspect of the

design. It is this aspect of the design which VI has mas-

tered through many years of experience.

The clock recovery process can be viewed as a band-

pass filter operation, accomplished either through a

SAW filter or through the composite effect of a closed

loop system (PLL). Most clock recovery devices

employ a phase lock loop architecture, which employs

a phase detector and loop amplifier to lock a free run-

ning VCO to the input signal. At lower data rates PLL

designs provide acceptable performance, but as data

rate increase, the ability to control critical loop gain

parameters over environmental extremes becomes

exceedingly difficult.

The accuracy and stability of the bandpass character-

istic determines how effectively the process will com-

ply with stringent SONET/SDH jitter requirements.

The TRU2500 offers superior jitter transfer, jitter toler-

ance and jitter generation performance because its

bandpass characteristic is prescribed by a precision

quartz SAW filter which can be precisely controlled

and accurately reproduced in volume production.

The circuit architecture of the clock recovery path is

shown in Figure 2. Figure 3. illustrates the time

domain waveform and its associated frequency

domain spectrum at various points in the path. Since

the input NRZ data stream (A) has a null at the clock

frequency, non-linear processing of the signal is

required to generate spectral content at the clock rate.

The circuit uses a microstrip line to delay the data 1/2

of a bit period. The data and delayed data are then fed

through an exclusive or-gate to produce a pulse at

each data transition. This signal then has a strong

spectral peak at the desired clock rate (B) and can be

viewed in the time domain as a clock signal with miss-

ing pulses. The pulse train is then filtered and shaped

prior to the SAW filter to provide optimum perfor-

mance. The SAW filters this signal to provide a contin-

uous sine wave (C) with compliant jitter characteristics.

This signal is amplified and becomes both the output

clock and the retiming signal for the decision circuit.

Due to careful attention to pre-filtering and shaping,

SAW filter bandpass characteristics, and the elimina-

tion of feedback loop clock to data alignment control,

the TRU2500 is able to offer output jitter performance

as low as 2psRMS, a level not achieved by phase

locked loop designs.

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TRU2500-L | Telecomm/Datacomm |

| TRU600A-SERIES | Peripheral IC |

| TRW2307 | Bipolar NPN UHF/Microwave Transisitor |

| TRX-IS | CALIBRATOR MULTIFUNCTION |

| TS182H | SACK TRUCK HEAVY DUTY FOLDIN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TRU3 | 制造商:Ssac 功能描述:Electromechanical Relay SPDT 10A 19V to 30VDC 19V to 264VAC Plug-In |

| TRU5336 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| TRU-600 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRU-600 |

| TRU6810SL | 制造商:TRU 功能描述: |

| TRU-7002-0001-01 | 制造商:TRU 功能描述:RF COAXIAL PANEL MOUNT CONNECTOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。