參數資料

| 型號: | TRF3750IRGPRG4 |

| 廠商: | Texas Instruments |

| 文件頁數: | 15/37頁 |

| 文件大小: | 0K |

| 描述: | IC PLL FREQ SYNTHESIZER 20-QFN |

| 標準包裝: | 1,000 |

| 類型: | PLL 頻率合成器 |

| PLL: | 無 |

| 輸入: | 時鐘 |

| 輸出: | 時鐘 |

| 電路數: | 1 |

| 比率 - 輸入:輸出: | 2:1 |

| 差分 - 輸入:輸出: | 是/無 |

| 頻率 - 最大: | 2.4GHz |

| 除法器/乘法器: | 是/無 |

| 電源電壓: | 3 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 20-VFQFN 裸露焊盤 |

| 供應商設備封裝: | 20-QFN 裸露焊盤(4x4) |

| 包裝: | 帶卷 (TR) |

| 配用: | TRF3750T-1900EVM-ND - TRF3750T-1900EVM TRF3750Q1900EVM-ND - TRF3750Q1900EVM 296-20836-ND - EVALUATION MOD FOR CDCM7005-QFN 296-20835-ND - EVALUATION MOD FOR CDCM7005-BGA 296-20834-ND - EVALUATION MOD FOR CDC7005-QFN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

TRF3750

SLWS146B MARCH 2004 REVISED AUGUST 2007

www.ti.com

22

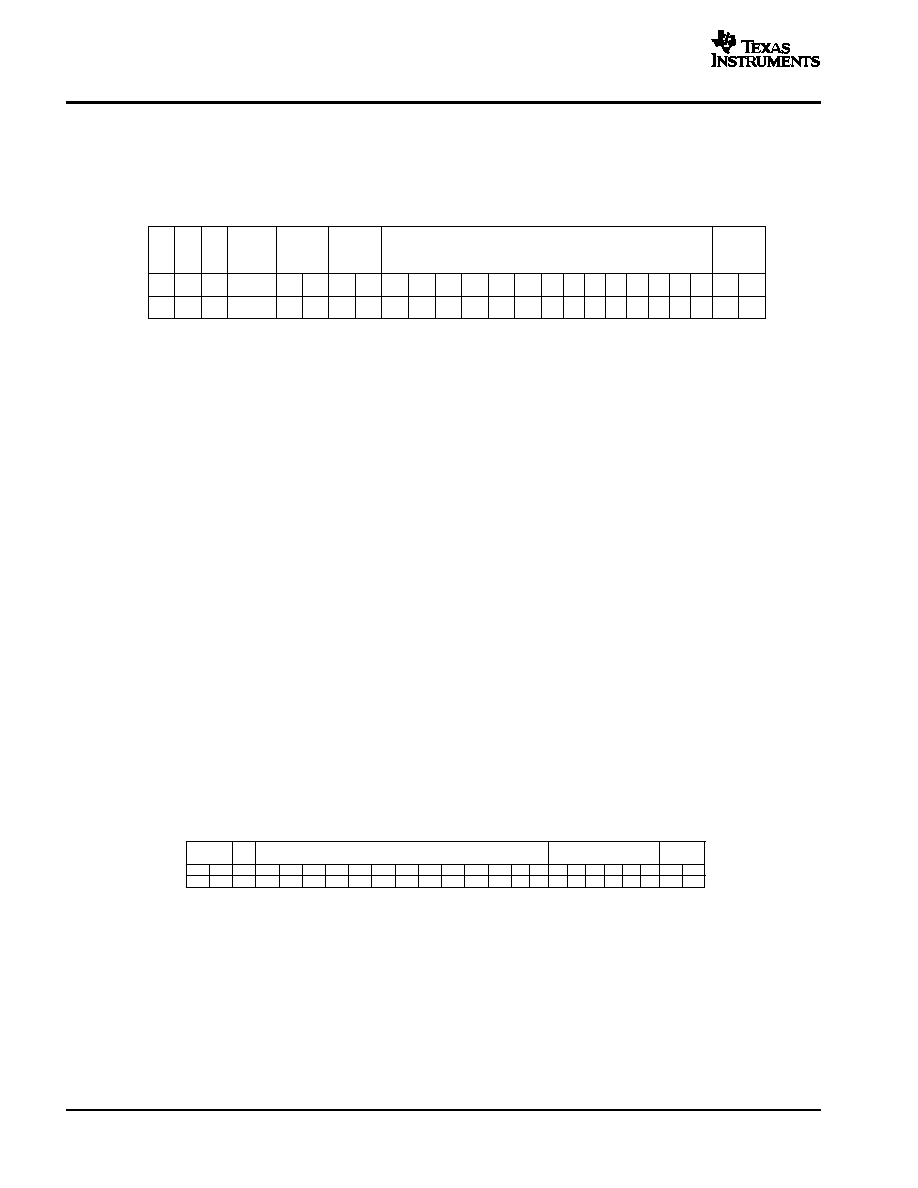

R Counter Latch

By selecting (0,0) for the control bits DB0 and DB1, the R counter latch is selected. Table 7 shows the setup

of the R counter latch.

Table 7. R Counter Latch

Reserved

Lock

Detect

Precision

Test

Mode Bits

Anti

Backlash

Width

Control

Bits

DB23 DB22 DB21

DB20

DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

X

DLY SYNC

LDP

T2

T1 ABP2 ABP1 R14 R13 R12 R11 R10

R9

R8 R7 R6 R5 R4 R3 R2 R1 C2(0) C1(0)

14-Bit Reference Counter; R

DLY SYNC

R Value

This latch is used primarily to select the R divider for the input reference signal (REFIN). DB2 through DB15

are used to select the chosen value for the 14-bit counter. DB2 is the LSB and DB15 the MSB.

Anti-backlash Pulse

DB16 and DB17 can be used to select the width of the anti-backlash pulse in the PFD. In any PFD

implementation, there is an inherent risk of backlash, a phenomenon that can occur when the device is almost

in lock. In order to ensure that there are always pulses coming out of the charge pump and that therefore the

VCO cannot drift out of lock, the TRF3750 employs an anti-backlash pulse. The user can select the width of

the anti-backlash pulse; the values allowed are 1.5 ns, 3 ns, and 6 ns.

Lock Detect Precision

Setting DB20 of the R counter latch to 0 results in a precision of three cycles for the lock detect, while setting

it to 1 results in a precision of five cycles.

Sync / Delay

DB2122 control the sync/delay operation of the device. If DB21 is 0, then the device is in normal operation.

Assuming DB21 is set to 1, setting DB22 to 0 utilizes a non-delayed form of the RF signal for the

resynchronization of the prescaler output, whereas setting DB22 to 1 utilizes a delayed form.

Reserved Bits

Bits DB18, DB19 and DB23 of the R counter latch are reserved. It is recommended to keep those bits 0 for

normal operation.

N Counter Latch

Setting (DB1, DB0) = (0,1) for the latch control bits selects the N counter latch. Table 8 shows the setup of the

N counter latch.

Table 8. N Counter Latch

Reserved

CP

Gain

Control

Bits l

DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

G1 B13 B12 B11 D10

B9

B8

B7

B6

B5

B4

B3

B2 B1 A6 A5 A4 A3 A2 A1 C2(0) C1(0)

X

13-Bit B Counter

6-Bit B Counter

A Counter

The 6 bits DB2DB7 control the value of the A counter. The valid range is from 0 to 63. For example,

programming (DB7, DB6, DB5, DB4, DB3,DB2) = (0,0,0,0,1,0) results in a value of 2 for the A counter.

B Counter

The 13 bits DB8DB20 of the N counter latch control the value of the B counter. The valid range is from 3 to

8191. For example, (DB20, DB19, …, DB10, DB9, DB8) = (0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 0, 0) results in a value

of 4 for the B counter.

Charge Pump Gain

DB21 of the N counter latch determines when the TRF3750 enters Fastlock Mode. When this bit is 1, the device

switches into fastlock and when this bit is 0, the device exits fastlock (fastlock mode 1).

相關PDF資料 |

PDF描述 |

|---|---|

| TRF3750IRGPR | IC PLL FREQ SYNTHESIZER 20-QFN |

| V375A48T600BF | CONVERTER MOD DC/DC 48V 600W |

| M83723/74W22197 | CONN RCPT 19POS JAM NUT W/PINS |

| V375A48T600BL3 | CONVERTER MOD DC/DC 48V 600W |

| V375A48T600BL2 | CONVERTER MOD DC/DC 48V 600W |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TRF3750Q1900EVM | 功能描述:射頻開發(fā)工具 TRF3750Q1900 Eval Mod RoHS:否 制造商:Taiyo Yuden 產品:Wireless Modules 類型:Wireless Audio 工具用于評估:WYSAAVDX7 頻率: 工作電源電壓:3.4 V to 5.5 V |

| TRF3750Q2100EVM | 制造商:Texas Instruments 功能描述:TRF3750Q2100 EVAL - Bulk |

| TRF3750Q900EVM | 制造商:Texas Instruments 功能描述:TRF3750Q900 EVAL - Bulk |

| TRF3750T-1900EVM | 功能描述:射頻開發(fā)工具 TRF3750T-1900 Eval Mod RoHS:否 制造商:Taiyo Yuden 產品:Wireless Modules 類型:Wireless Audio 工具用于評估:WYSAAVDX7 頻率: 工作電源電壓:3.4 V to 5.5 V |

| TRF3761 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:INTEGER-N PLL WITH INTEGRATED VCO |

發(fā)布緊急采購,3分鐘左右您將得到回復。