- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > T8534 T8533/34 Quad Programmable Line Card Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | T8534 |

| 英文描述: | T8533/34 Quad Programmable Line Card Signal Processor |

| 中文描述: | T8533/34四線卡可編程信號(hào)處理器 |

| 文件頁(yè)數(shù): | 20/48頁(yè) |

| 文件大小: | 890K |

| 代理商: | T8534 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

Preliminary Data Sheet

July 2001

Signal Processor

T8533/34 Quad Programmable Line Card

20

Agere Systems Inc.

Functional Description

(continued)

The Control Interface

(continued)

Fast Scan Mode

The fast scan mode allows a single byte command to read two SLIC control leads for all four channels with a

1-byte reply. This mode significantly speeds up the normal scanning for off-hook, ring trip, and ring ground detec-

tion. This special command sequence allows the controlling microprocessor to fast scan 2 bits in the SLIC control

byte of each of the four channels. The command code is (00000010)

2

, there are no start address or length fields.

The command returns only a single byte of data, formatted as shown in Table 9.

Table 7. Bit Assignments for Fast Scan Mode

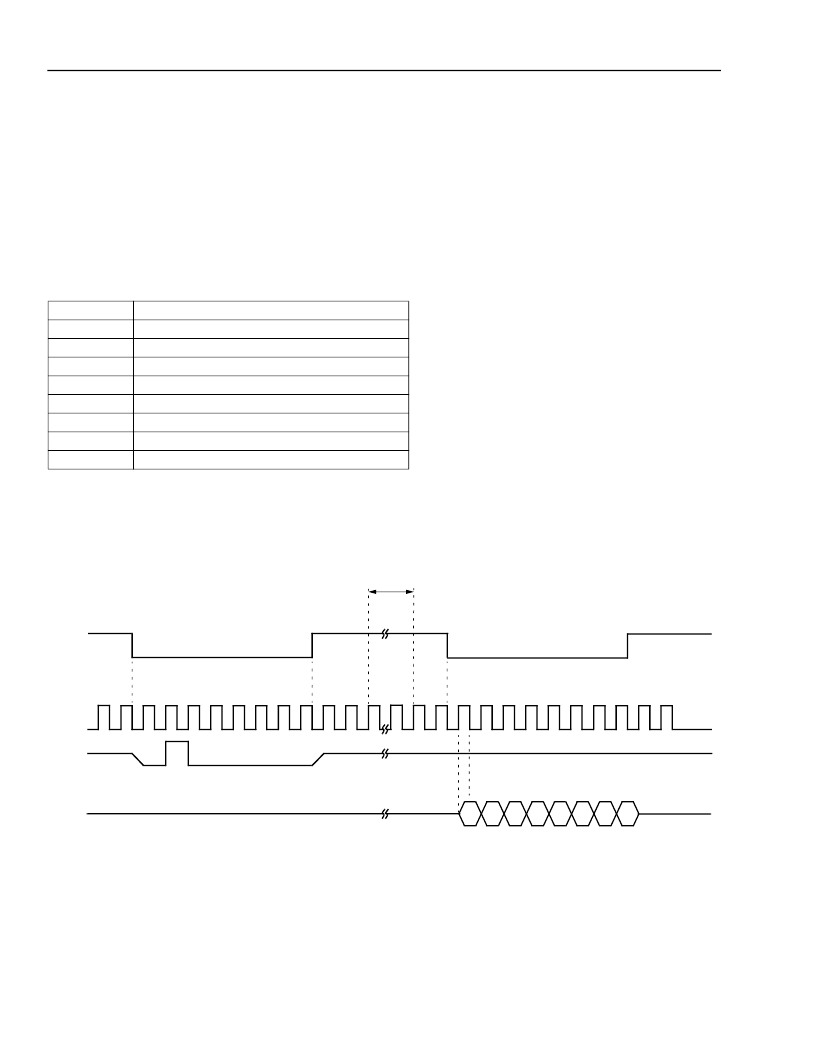

The circuit select in the command structure (Figure 5) is not used for this special single-byte command. The rules

for toggling chip select apply as for the read command. Figures 15—18 illustrate normal or byte-by-byte operation

with continuous or gapped DCLKs.

0125

* Provide sufficient wait time to access read data. Provide sufficient DCLK cycles to effectively wait

≥

1.5

μ

s after the second full DCLK cycle

and before the second to last full DCLK cycle. DCLK operation of 4.096 MHz would require 10 cycles of DCLK between COMMAND and

DATA. The first two DCLK cycles, when CS goes high, processes the command. A wait is then required to access the read data. Two final

DCLK cycles are required to process the read data.

Two or more DCLK cycles are required before the start of a new command frame.

Figure 15. Fast Scan, Normal Mode (Continuous DCLK)

Bit

Reported Status

0 (LSB)

1

2

3

4

5

6

7 (MSB)

Channel 0, bit 0 (ckt a, address 160, bit 0)

Channel 0, bit 1 (ckt a, address 160, bit 1)

Channel 1, bit 0 (ckt b, address 160, bit 0)

Channel 1, bit 1 (ckt b, address 160, bit 1)

Channel 2, bit 0 (ckt c, address 160, bit 0)

Channel 2, bit 1 (ckt c, address 160, bit 1)

Channel 3, bit 0 (ckt d, address 160, bit 0)

Channel 3, bit 1 (ckt d, address 160, bit 1)

1

2

3

CS

DCLK

DI

COMMAND

DATA

4

5

DO

WAIT

≥

1.5

μ

s

0

1

2

3

4

5

6

7

6

7

0

1

2

3

4

5

6

7

0

*

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8535B | T8535B/T8536B Quad Programmable Codec |

| T8536B | T8535B/T8536B Quad Programmable Codec |

| T8538B | T8538B Quad Programmable Codec |

| T923CFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

| T923WFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8535B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8536B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8538B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8538B Quad Programmable Codec |

| T85471G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85471J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。