- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361357 > T71L6808A (TM Technology, Inc.) Octal 10/100 Switch with Embedded Memory PDF資料下載

參數(shù)資料

| 型號: | T71L6808A |

| 廠商: | TM Technology, Inc. |

| 英文描述: | Octal 10/100 Switch with Embedded Memory |

| 中文描述: | 八路10/100交換機嵌入式存儲器 |

| 文件頁數(shù): | 13/23頁 |

| 文件大小: | 335K |

| 代理商: | T71L6808A |

TE

CH

tm

Preliminary T71L6808A

Taiwan Memory Technology, Inc. reserves the right

P. 13

to change products or specifications without notice.

Publication Date:May. 2001

Revision:0.A

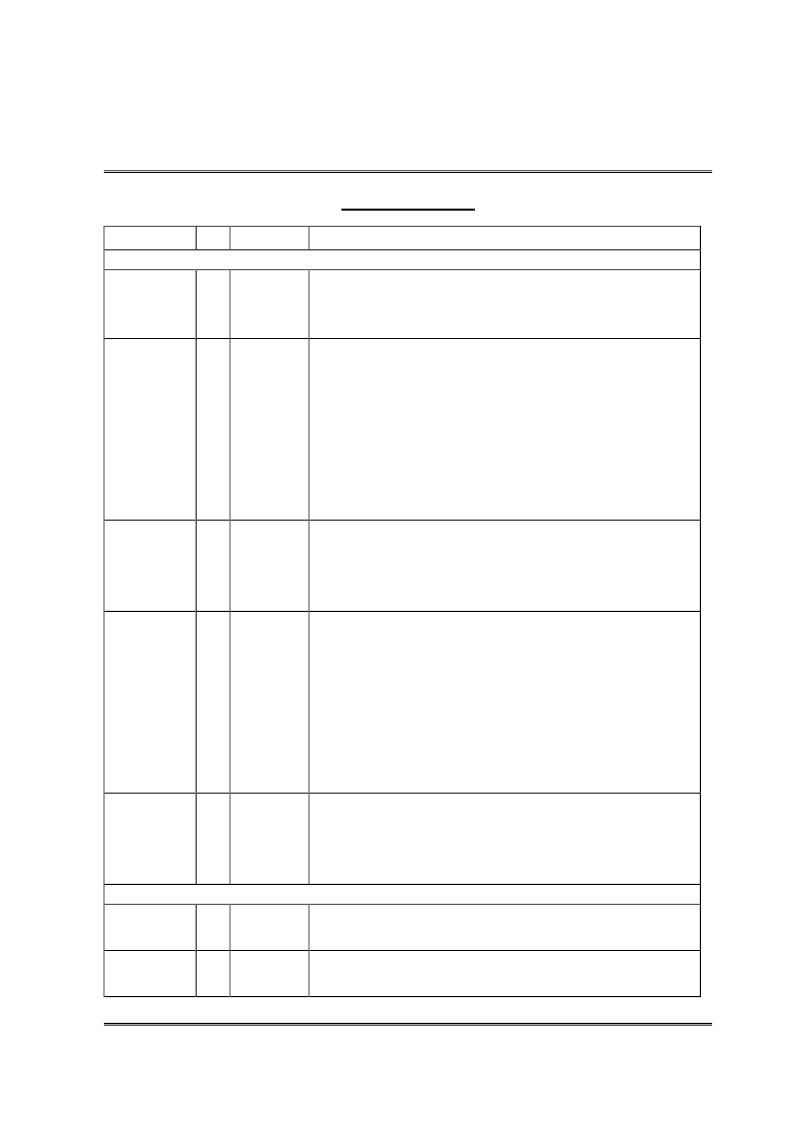

Pin Description

Symbol

RMII Interface

REFCLK

I/O

Pin No.

Function

I

47

Reference Clock.

REFCLK is a 50MHz clock that provides the timing reference

for CRS_DV, RXD[1:0], TX_EN and TXD[1:0].

Transmit Data.

TXD[1:0] shall transition synchronously with respect to

REFCLK. When TX_EN is asserted, TXD[1:0] are accepted for

transmission by the PHY.

TXD[1:0][A]

TXD[1:0][B]

TXD[1:0][C]

TXD[1:0][D]

TXD[1:0][E]

TXD[1:0][F]

TXD[1:0][G]

TXD[1:0][H]

TXE[A:H]

O

8,9

14,15

26,27

59,60

69,70

77,78

87,88

93,94

7,13,24,58

68,76,86,92

O

Transmit Enable.

TX_EN indicates that the MAC is presenting di-bits on

TXD[1:0] on the RMII for transmission. It shall transmit

synchronously with REFCLK.

Receive Data[1:0].

RXD[1:0] shall transition synchronously to REFCLK. For each

clock period in which CRS_DV is asserted, RXD[1:0] transfers

two bits of recovered data from the PHY.

RXD[1:0][A]

RXD[1:0][B]

RXD[1:0][C]

RXD[1:0][D]

RXD[1:0][E]

RXD[1:0][F]

RXD[1:0][G]

RXD[1:0][H]

CRSDV[A:H]

I

11,12

19,20

29,31

62,63

73,74

80,81

90,91

97,98

10,18,28,61

72,79,89,96

I

Carrier Sense/Receive Data Valid.

CRS_DV shall be asserted by the PHY when the receive

medium is non-idle and asserted asynchronously on detection of

carrier due to the criteria relevant to the operating mode.

System Pins

RST#

I

53

Reset.

Asynchronous active low reset signal

System Clock.

System clock, 50MHz

SYSCLK

I

119

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T71L6816A | Sixteen-port 10/100 Switch |

| T81L0003A | Reduced I/O 8-bit MCU |

| T81L0003A-AK | Reduced I/O 8-bit MCU |

| T81L0003A-BD | Reduced I/O 8-bit MCU |

| T81L0003A-BK | Reduced I/O 8-bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T71L6816A | 制造商:TMT 制造商全稱:TMT 功能描述:Sixteen-port 10/100 Switch |

| T71U5D132-12 | 制造商:TE Connectivity 功能描述: |

| T71U5D132-24 | 制造商:TE Connectivity 功能描述: |

| T71U5D132-6 | 制造商:TE Connectivity 功能描述: |

| T71U5D164-12 | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。