- 您現在的位置:買賣IC網 > PDF目錄98142 > SST89E54RC-33-C-PIE 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 PDF資料下載

參數資料

| 型號: | SST89E54RC-33-C-PIE |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MS-011AC, DIP-40 |

| 文件頁數: | 38/57頁 |

| 文件大小: | 652K |

| 代理商: | SST89E54RC-33-C-PIE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

Data Sheet

FlashFlex MCU

SST89E52RC / SST89E54RC

43

2007 Silicon Storage Technology, Inc.

S71259-04-000

1/07

10.0 POWER-SAVING MODES

The device provides two power saving modes of operation

for applications where power consumption is critical. The

two modes are idle and power-down, see Table 10-1.

In addition to these two power saving modes, users can

choose to set the device to run at one of four slower clock

rates to reduce power consumption. See Section 11.3,

Another option is to turn off the clocks by individual func-

tional blocks, please refer to Section 3.5, the PMC register

definition, for detailed information.

10.1 Idle Mode

Idle mode is entered setting the IDL bit in the PCON regis-

ter. In idle mode, the program counter (PC) is stopped. The

system clock continues to run and all interrupts and periph-

erals remain active. The on-chip RAM and the special func-

tion registers hold their data during this mode.

The device exits idle mode through either a system inter-

rupt or a hardware reset. Exiting idle mode via system

interrupt, the start of the interrupt clears the IDL bit and

exits idle mode. After exit the Interrupt Service Routine, the

interrupted program resumes execution beginning at the

instruction immediately following the instruction which

invoked the idle mode. A hardware reset starts the device

similar to a power-on reset.

10.2 Power-down Mode

The power-down mode is entered by setting the PD bit in

the PCON register. In the power-down mode, the clock is

stopped and external interrupts are active for level sensitive

interrupts only. SRAM contents are retained during power-

down, the minimum VDD level is 2.0V.

The device exits power-down mode through either an

enabled external level sensitive interrupt or a hardware

reset. The start of the interrupt clears the PD bit and exits

power-down. Holding the external interrupt pin low restarts

the oscillator, the signal must hold low at least 1024 clock

cycles before bringing back high to complete the exit. Upon

interrupt signal restored to logic VIH, the interrupt service

routine program execution resumes beginning at the

instruction immediately following the instruction which

invoked power-down mode. A hardware reset starts the

device similar to power-on reset.

To exit properly out of power-down, the reset or external

interrupt should not be executed before the VDD line is

restored to its normal operating voltage. Be sure to hold

VDD voltage long enough at its normal operating level for

the oscillator to restart and stabilize (normally less than

10 ms).

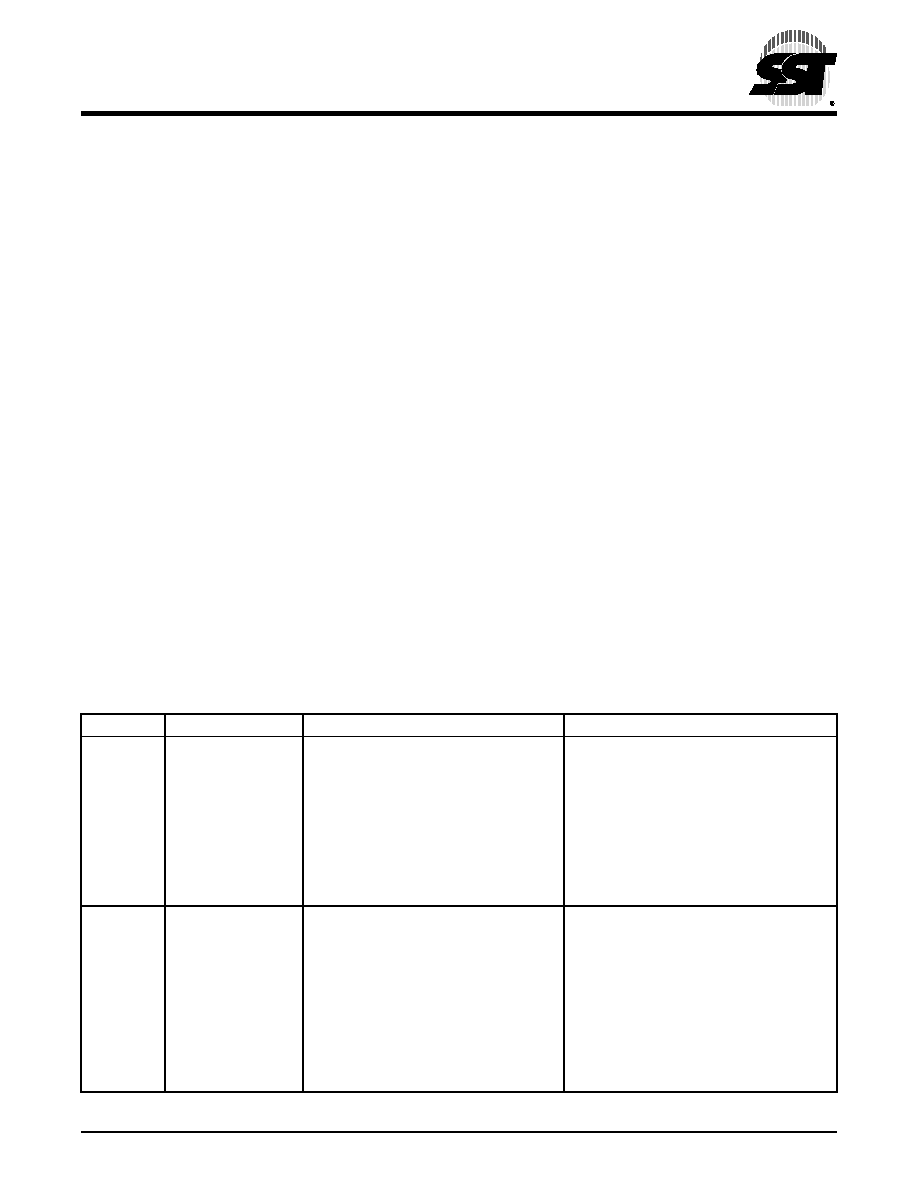

TABLE

10-1: Power Saving Modes

Mode

Initiated by

State of MCU

Exited by

Idle

Software

(Set IDL bit in PCON)

MOV PCON, #01H;

CLK is running.

Interrupts, serial port and

timers/counters are active.

Program Counter is stopped.

ALE and PSEN# signals at a

HIGH level during Idle.

All registers remain unchanged.

Enabled interrupt or hardware reset.

Start of interrupt clears IDL bit and exits idle

mode, after the ISR RETI instruction, program

resumes execution beginning at the instruction

following the one that invoked idle mode. A user

could consider placing two or three NOP

instructions after the instruction that invokes idle

mode to eliminate any problems. A hardware

reset restarts the device similar to a power-on

reset.

Power-down Software

(Set PD bit in PCON)

MOV PCON, #02H;

CLK is stopped.

On-chip SRAM and SFR

data is maintained.

ALE and PSEN# signals at a

LOW level during power -down.

External Interrupts are only active for

level sensitive interrupts, if enabled.

Enabled external level sensitive interrupt or

hardware reset. Start of interrupt clears PD

bit and exits power-down mode, after the

ISR RETI instruction program resumes exe-

cution beginning at the instruction following

the one that invoked power-down mode. A

user could consider placing two or three

NOP instructions after the instruction that

invokes power-down mode to eliminate any

problems. A hardware reset restarts the

device similar to a power-on reset.

T10-1.0 1259

相關PDF資料 |

PDF描述 |

|---|---|

| SST89E54RC-33-C-NJE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQCC44 |

| SST89E52RC-33-C-NJE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQCC44 |

| SST89E52RC-33-C-PIE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| SST89V516RD-33-I-PIE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| SST89V516RD-33-C-PI | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SST89E54RD | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex MCU |

| SST89E54RD2 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E54RD2/RD | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E54RD2-33-C-NI | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E54RD2-33-C-NIE1 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復。