- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373433 > SN54ABT32500 (Texas Instruments, Inc.) 36-Bit Universal Bus Transceivers With 3-State Outputs(36位通用總線收發(fā)器(三態(tài)輸出)) PDF資料下載

參數(shù)資料

| 型號: | SN54ABT32500 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 36-Bit Universal Bus Transceivers With 3-State Outputs(36位通用總線收發(fā)器(三態(tài)輸出)) |

| 中文描述: | 36位通用總線收發(fā)器與三態(tài)輸出(36位通用總線收發(fā)器(三態(tài)輸出)) |

| 文件頁數(shù): | 1/8頁 |

| 文件大小: | 135K |

| 代理商: | SN54ABT32500 |

SN54ABT32500, SN74ABT32500

36-BIT UNIVERSAL BUS TRANSCEIVERS

WITH 3-STATE OUTPUTS

SCBS462 – JUNE 1992–REVISED OCTOBER 1992

Latch-Up Performance Exceeds 500 mA Per

JEDEC Standard JESD-17

Typical V

OLP

(Output Ground Bounce)

< 0.8 V at V

CC

= 5 V, T

A

= 25

°

C

Distributed V

CC

and GND Pin Configuration

Minimizes High-Speed Switching Noise

High-Drive Outputs (–32-mA I

OH

,

64-mA I

OL

)

Packaged in 100-Pin Plastic Shrink Quad

Flat Pack (SQFP) With 14

×

14-mm Package

Body Using 0.5-mm Lead Pitch

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Copyright

1992, Texas Instruments Incorporated

1

Members of the Texas Instruments

Widebus+

Family

State-of-the-Art EPIC-

ΙΙ

B

BiCMOS Design

Significantly Reduces Power Dissipation

UBT

(Universal Bus Transceiver)

Combines D-Type Latches and D-Type

Flip-Flops for Operation in Transparent,

Latched, or Clocked Mode

ESD Protection Exceeds 2000 V Per

MIL-STD-883C, Method 3015; Exceeds

200 V Using Machine Model (C = 200 pF,

R = 0)

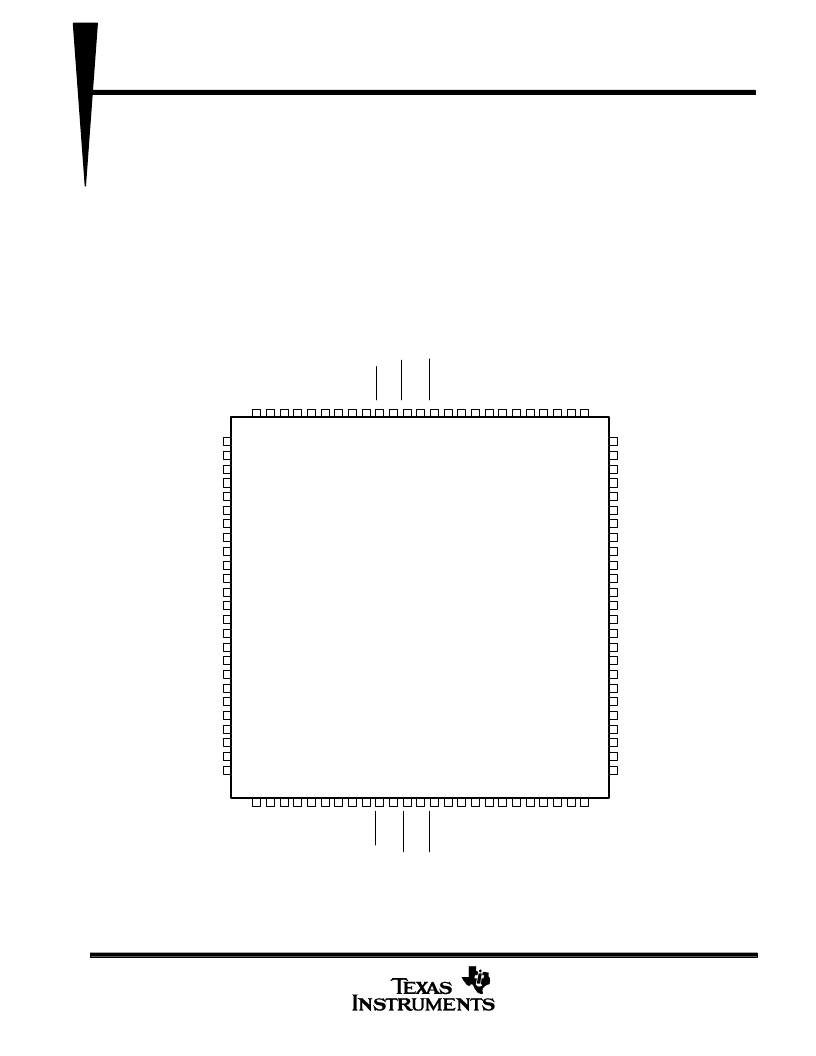

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

SN74ABT32500 . . . PZ PACKAGE

(TOP VIEW)

2A10

2A9

GND

2A8

2A7

2A6

2A5

GND

2A4

2A3

2A2

2A1

V

CC

1A1

1A2

1A3

1A4

GND

1A5

1A6

1A7

1A8

GND

1A9

1A10

2B10

2B9

GND

2B8

2B7

2B6

2B5

GND

2B4

2B3

2B2

2B1

V

CC

1B1

1B2

1B3

1B4

GND

1B5

1B6

1B7

1B8

GND

1B9

1B10

2

2

2

V

C

G

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

G

2

2

2

G

1

1

1

1

1

1

1

1

1

1

1

1

1

G

1

1

1

1

V

C

50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

ABT32500–2

Widebus+, EPIC-

ΙΙ

B, and UBT are trademarks of Texas Instruments Incorporated.

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74ABT32500 | 36-Bit Universal Bus Transceivers With 3-State Outputs(36位通用總線收發(fā)器(三態(tài)輸出)) |

| SN54ABT3614HFP | 64 】 36 】 2 CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY WITH BUS MATCHING AND BYTE SWAPPING |

| SN54ABT3614PCB | 64 】 36 】 2 CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY WITH BUS MATCHING AND BYTE SWAPPING |

| SN54ABT373FK | OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN54ABT373J | OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN54ABT32501 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:36-BIT UNIVERSAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN54ABT32543 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:36-BIT REGISTERED BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN54ABT3614 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:64 】 36 】 2 CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY WITH BUS MATCHING AND BYTE SWAPPING |

| SN54ABT3614HFP | 制造商:Texas Instruments 功能描述:FIFO SYNC DUAL BI-DIR 64 X 36 X 2 132CFPAK - Bulk |

| SN54ABT3614PCB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:64 】 36 】 2 CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY WITH BUS MATCHING AND BYTE SWAPPING |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。