- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25644 > SI5338N-AXXXXXGM (SILICON LABORATORIES) 700 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC24 PDF資料下載

參數(shù)資料

| 型號: | SI5338N-AXXXXXGM |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 700 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC24 |

| 封裝: | 4 X 4 MM, ROHS COMPLIANT, MO-220VGGD-8, QFN-24 |

| 文件頁數(shù): | 5/42頁 |

| 文件大小: | 380K |

| 代理商: | SI5338N-AXXXXXGM |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Si5338

Rev. 1.0

13

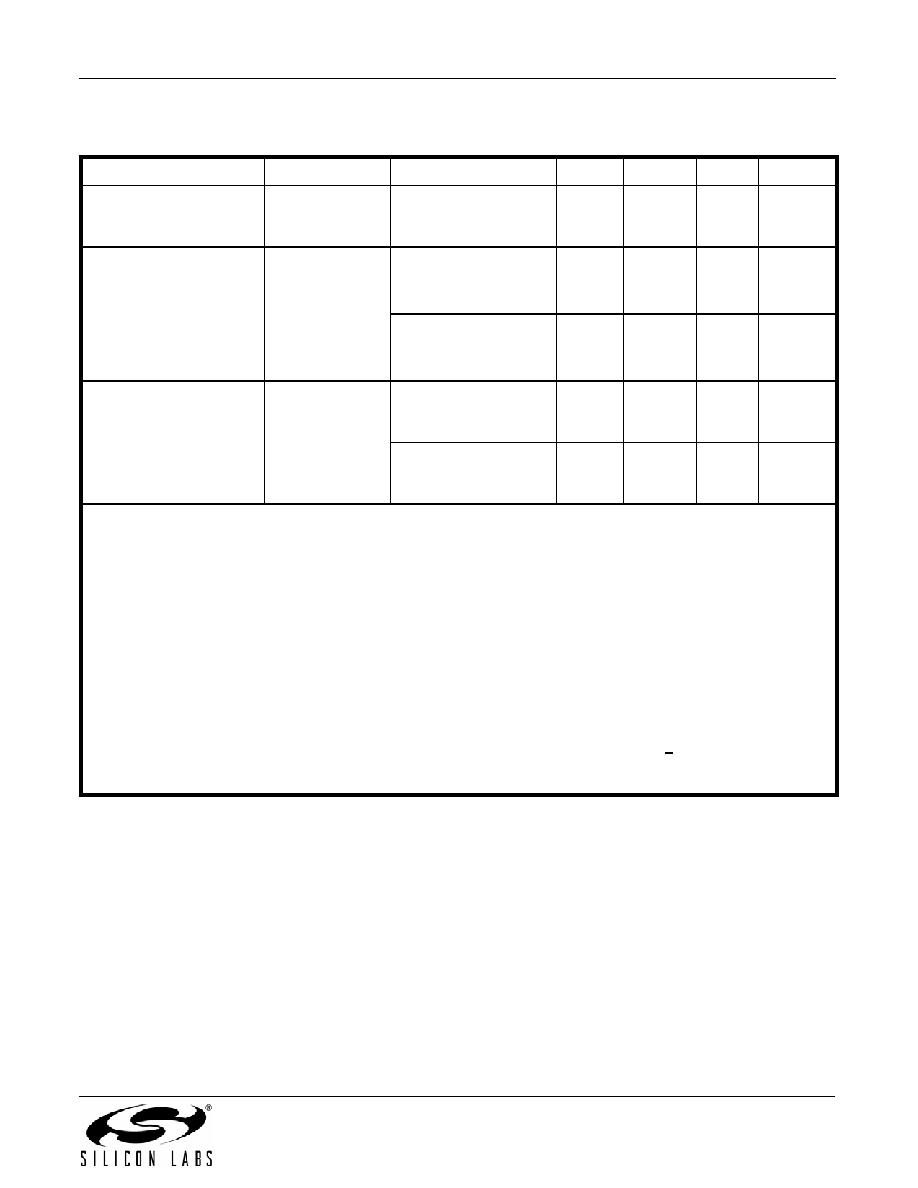

Random Jitter

(12kHz–20MHz)

RJ

Output and feedback

MultiSynth in integer or

fractional mode7

—

0.7

1.5

ps RMS

Deterministic Jitter

DJ

Output MultiSynth

operated in fractional

mode7

—3

15

ps pk-pk

Output MultiSynth

operated in integer

mode7

—2

10

ps pk-pk

Total Jitter

(12kHz–20MHz)

TJ =DJ+14xRJ

(See Note 9)

Output MultiSynth

operated in fractional

mode7

—

13

36

ps pk-pk

Output MultiSynth

operated in integer

mode7

—

12

20

ps pk-pk

Table 12. Jitter Specifications1,2,3 (Continued)

(VDD = 1.8 V –5% to +10%, 2.5 V ±10%, or 3.3 V ±10%, TA = –40 to 85 °C)

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

Notes:

1. All jitter measurements apply for LVDS/HCSL/LVPECL output format with a low noise differential input clock and are

made with an Agilent 90804 oscilloscope. All RJ measurements use RJ/DJ separation.

2. For best jitter performance, keep the single ended clock input slew rates at Pins 3 and 4 more than 1.0 V/ns and the

differential clock input slew rates more than 0.3 V/ns.

3. All jitter data in this table is based upon all output formats being differential. When single-ended outputs are used, there

is the potential that the output jitter may increase due to the nature of single-ended outputs. If your configuration

implements any single-ended output and any output is required to have jitter less than 3 ps rms, contact Silicon Labs

for support to validate your configuration and ensure the best jitter performance. In many configurations, CMOS

outputs have little to no effect upon jitter.

4. DJ for PCI and GbE is < 5 ps pp

5. Output MultiSynth in Integer mode.

6. All output clocks 100 MHz HCSL format. Jitter is from the PCIE jitter filter combination that produces the highest jitter.

See AN562 for details.

7. Input frequency to the Phase Detector between 25 and 40 MHz and any output frequency > 5MHz.

8. Measured in accordance with JEDEC standard 65.

9. Rj is multiplied by 14; estimate the pp jitter from Rj over 212 rising edges.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SL28540ALCT | OTHER CLOCK GENERATOR, QCC56 |

| SL5504 | 1 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

| SL5582.3S | 1 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

| SLA-360MTT32S | T-1 SINGLE COLOR LED, YELLOW GREEN, 3.1 mm |

| SLA-570LT3FXH | T-1 3/4 SINGLE COLOR LED, RED, 5 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI5338N-B01504-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Bulk |

| SI5338N-B01504-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5338N-B01552-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Bulk |

| SI5338N-B01552-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5338N-B01598-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。