- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372130 > SCN68652AC2F40 (NXP SEMICONDUCTORS) Multi-protocol communications controller MPCC PDF資料下載

參數(shù)資料

| 型號: | SCN68652AC2F40 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Multi-protocol communications controller MPCC |

| 中文描述: | 1 CHANNEL(S), 2M bps, MULTI PROTOCOL CONTROLLER, CDIP40 |

| 封裝: | CERAMIC, DIP-40 |

| 文件頁數(shù): | 5/28頁 |

| 文件大小: | 651K |

| 代理商: | SCN68652AC2F40 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

Philips Semiconductors

Product specification

SCN2652/SCN68652

Multi-protocol communications controller (MPCC)

1995 May 01

5

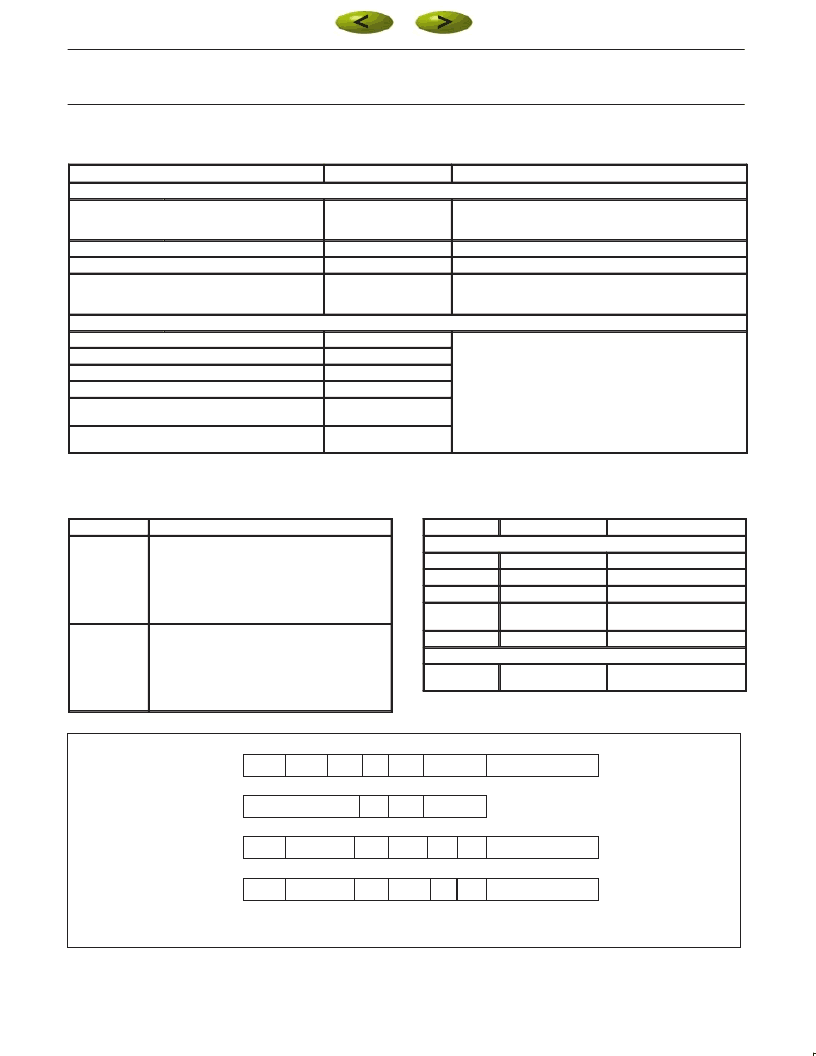

Table 1.

Register Access

REGISTERS

NO. OF BITS

DESCRIPTION*

Addressable

PCSAR

Parameter control sync/

address register

16

PCSAR

H

and PCR contain parameters common to the

receiver and transmitter. PCSAR

L

contains a programmable

SYNC character (BCP) or secondary station address (BOP).

RDSR

H

contains receiver status information.

RDSR

L

= RxDB contains the received assembled character.

TDSR

H

contains transmitter command and status

information. TDSRL = TxDB contains the character to be

transmitted

PCR

RDSR

Parameter control register

Receive data/status register

8

16

TDSR

Transmit data/status register

16

Non-Addressable

CCSR

HSR

RxSR

TxSR

Control character shift register

Holding shift register

Receiver shift register

Transmitter shift register

Receiver CRC accumulation

register

Transmitter CRC generation

register

8

16

8

8

These registers are used for character assembly (CSSR,

HSR, RxSR), disassembly (TxSR),

accumulation/generation (RxCRC, TxCRC).

RxCRC

16

TxCRC

16

NOTES:

*H = High byte – bits 15–8

L = Low byte – bits 7–0

Table 2.

CHARACTER

FCS

Error Control

DESCRIPTION

Frame check sequence is transmitted/received

as 16 bits following the last data character of a

BOP message. The divisor is usually

CRC–CCITT (X

16

+ X

12

+ X

5

+ 1) with dividend

preset to 1’s but can be other wise determined

by ECM. The inverted remainder is transmitter as

the FCS.

Block check character is transmitted/received as

two successive characters following the last data

character of a BCP message. The polynomial is

CRC–16 (X

16

+ X

15

+ X

2

+ 1) or CRC–CCITT

with dividend preset to 0’s (as specified by

ECM). The true remainder is transmitted as the

BCC.

BCC

Table 3.

OPERATION

BOP

FLAG

ABORT

Special Characters

BIT PATTERN

FUNCTION

01111110

11111111 generation

01111111 detection

Frame message

Terminate communication

GA

01111111

Terminate loop mode

repeater function

Secondary station address

Address

BCP

(PCSAR

L

)

1

SYNC

(PCSAR

L

) or

(TxDB)

2

generation

Character synchronization

NOTES:

1. ( ) = contents of.

2. For IDLE = 0 or 1 respectively.

APA

PCSAR

PCR

RDSR

TDSR

15

PROTO

14

SS/GA

13

SAM

12

IDLE

11

E C M

10

9

8

S/AR

7

6

5

4

3

2 1

0

TxCL

15

14

13

12

11

RxCL

10

9

8

TxCLE

RxCLE

RERR

15

A B C

14

13

ROR

12

RAB/

GA

11

REOM

10

9

8

RxDB

RSOM

TERR

15

NOT DEFINED

14

13

TGA

12

TABORT

11

TEOM

10

9

8

TxDB

TSOM

NOTE:

Refer to Register Formats for mnemonics and description.

SD00059

Figure 3. Short Form Register Bit Formats

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCN26562C2A52 | Communications Controller |

| SCN26562C2N48 | Communications Controller |

| SCN2681AC1F40 | UART |

| SCN2681TC1A44A | UART |

| SCN2681TC1N40A | UART |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCN68652AC2N40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi-protocol communications controller MPCC |

| SCN68661 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

| SCN68681 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

| SCN68681C1A44 | 制造商:PHILIPS 功能描述:SCN68681C1A44 制造商:NXP Semiconductors 功能描述: 制造商:NXP Semiconductors 功能描述:UART, 44 Pin, Plastic, PLCC |

| SCN68681C1N40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。