- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376340 > SCANPSC110FLMQB (NATIONAL SEMICONDUCTOR CORP) SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) PDF資料下載

參數(shù)資料

| 型號(hào): | SCANPSC110FLMQB |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, CQCC28 |

| 封裝: | LCC-28 |

| 文件頁數(shù): | 3/29頁 |

| 文件大?。?/td> | 459K |

| 代理商: | SCANPSC110FLMQB |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

Table of Contents

(Continued)

TABLE 1. Glossary of Terms

(Continued)

Active Scan Chain

The Active Scan Chain refers to the scan chain configuration as seen by the test master at a given

moment. When a ’PSC110F is selected with all of its LSPs parked, the active scan chain is the

current scan bridge register only. When a LSP is unparked, the active scan chain becomes: TDI

B

→

the current ’PSC110F register

→

the local scan ring registers

→

a PAD bit

→

TDO

B

. Refer to

Table 4 for Unparked configurations of the LSP network.

Level 1 is the protocol used to address a ’PSC110F.

Level 2 is the protocol that is used once a ’PSC110F is selected. Level 2 protocol is IEEE Std.

1149.1 compliant when an individual ’PSC110F is selected.

A one bit register that is placed at the end of each local scan port scan-chain. The PAD bit

eliminates the prop delay that would be added by the ’PSC110F LSPN logic between TDI

Ln

and

TDO

L(n+1)

or TDO

B

by buffering and synchronizing the TDI

L

inputs to the falling edge of TCK

B

,

thus allowing data to be scanned at higher frequencies without violating set-up and hold times.

Least Significant Bit, the right-most position in a register (bit 0)

Most Significant Bit, the left-most position in a register

Level 1 Protocol

Level 2 Protocol

PAD

LSB

MSB

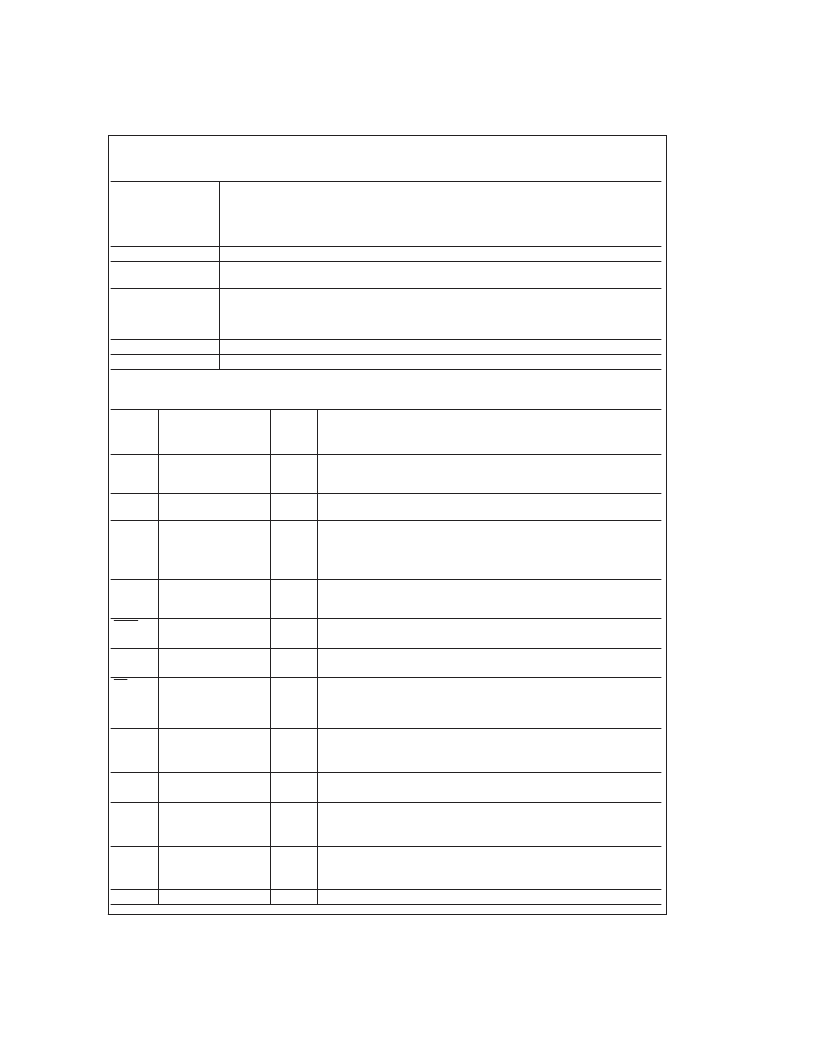

TABLE 2. Detailed Pin Description Table

Pin

#

(SOIC

& LCC)

10

Name

I/O

(Note 1)

Description

TMS

B

TTL Input w/Pull-Up

Resistor

BACKPLANE TEST MODE SELECT:

Controls sequencing through the TAP

Controller of the SCANPSC110F Bridge. Also controls sequencing of the TAPs

which are on the three (3) local scan chains.

BACKPLANE TEST DATA INPUT:

All backplane scan data is supplied to the

’PSC110F through this input pin.

BACKPLANE TEST DATA OUTPUT:

This output drives test data from the

’PSC110F and the local TAPs, back toward the scan master controller.

TDI

B

TTL Input w/Pull-Up

Resistor

TRI-STATEable,

32 mA/64 mA Drive,

Reduced-Swing,

Output

TTL Schmitt Trigger

Input

12

TDO

B

13

TCK

B

11

TEST CLOCK INPUT FROM THE BACKPLANE:

This is the master clock

signal that controls all scan operations of the ’PSC110F and of the three (3)

local scan ports.

TEST RESET:

An asynchronous reset signal (active low) which initializes the

’PSC110F logic.

TRST

TTL Input w/Pull-Up

Resistor

TTL Inputs

9

S

(0–5)

2, 3, 4,

5, 6, 7

1

SLOT IDENTIFICATION:

The configuration of these six (6) pins is used to

identify (assign a unique address to) each ’PSC110F on the system backplane.

OE

TTL Input

OUTPUT ENABLE for the Local Scan Ports, active low.

When high, this

active-low control signal TRI-STATEs all three local scan ports on the

’PSC110F, to enable an alternate resource to access one or more of the three

(3) local scan chains.

TEST DATA OUTPUTS:

Individual output for each of the three (3) local scan

ports.

TDO

L(1–3)

TRI-STATEable,

24 mA/24 mA

Drive Outputs

TTL Inputs w/Pull-Up

Resistors

TRI-STATEable,

24 mA/24 mA

Drive Outputs

TRI-STATEable,

24 mA/24 mA

Drive Output

Power Supply Voltage

15,19,

24

TDI

L(1–3)

18, 23,

27

16, 20,

25

TEST DATA INPUTS:

Individual scan data input for each of the three (3) local

scan ports.

TMS

L(1–3)

TEST MODE SELECT OUTPUTS:

Individual output for each of the three (3)

local scan ports. TMS

L

does

not

provide a pull-up resistor (which is assumed

to be present on a connected TMS input, per the IEEE 1149.1 requirement)

TCK

L(1–3)

17, 22,

26

LOCAL TEST CLOCK OUTPUTS:

Individual output for each of the three (3)

local scan ports. These are buffered versions of TCK

B

.

V

CC

8, 28

Power supply pins, 5.0V

±

10%.

S

www.national.com

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCANSTA101 | RES 30K OHM 1/16W 0.1% 0402 SMD |

| SCANSTA111SM | EMITTER IR 850NM 5MM RADIAL |

| SCANSTA111 | Enhanced SCAN bridge Multidrop Addressable IEEE 1149.1 (JTAG) Port |

| SCANSTA111MT | Enhanced SCAN bridge Multidrop Addressable IEEE 1149.1 (JTAG) Port |

| SCANSTA112 | 7-port Multidrop IEEE 1149.1 (JTAG) Multiplexer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCANPSC110FSC | 功能描述:特定功能邏輯 SCAN JTAG Port RoHS:否 制造商:Texas Instruments 產(chǎn)品: 系列:SN74ABTH18502A 工作電源電壓:5 V 封裝 / 箱體:LQFP-64 封裝:Tube |

| SCANPSC110FSCX | 功能描述:特定功能邏輯 SCAN JTAG Port RoHS:否 制造商:Texas Instruments 產(chǎn)品: 系列:SN74ABTH18502A 工作電源電壓:5 V 封裝 / 箱體:LQFP-64 封裝:Tube |

| SCANSTA101 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Low Voltage IEEE 1149.1 STA Master |

| SCANSTA101_06 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Low Voltage IEEE 1149.1 STA Master |

| SCANSTA101SM | 功能描述:接口 - 專用 RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。