- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379343 > SAF7843HL (NXP Semiconductors N.V.) One chip CD audio device with integrated MP3-WMA decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAF7843HL |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | One chip CD audio device with integrated MP3-WMA decoder |

| 封裝: | SAF7843HL/M295<SOT486-1 (LQFP144)|<<http://www.nxp.com/packages/SOT486-1.html<1<Always Pb-free,;SAF7849HL/M245<SOT486-1 (LQFP144)|<<http://www.nxp.com/packages/SOT486-1.h |

| 文件頁數(shù): | 29/93頁 |

| 文件大?。?/td> | 396K |

| 代理商: | SAF7843HL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

SAF784X_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 — 9 May 2008

29 of 93

NXP Semiconductors

SAF784x

One chip CD audio device with integrated MP3/WMA decoder

The first and last tap can be programmed via register PLLEqualiser.

Usable EFM bit clock range:

The channel bit clock frequency f

clk(bit)ch

must obey the

following constraints in relation to the system clock frequency f

clk(sys)

. The channel bit

clock frequency must always be:

less than f

clk(sys)

×

2 (Hz)

greater than f

clk(sys)

×

0.25 (Hz)

Therefore the range is: f

clk(sys)

×

0.25 < f

clk(bit)ch

< f

clk(sys)

×

2 (Hz)

A reliable bit detection is only possible within this range. If the input channel bit rate is

above f

clk(sys)

×

2 then the PLL will saturate to twice the system clock frequency.

Note that while these are theoretical limits, a real-life application should have a safety

margin. When the bit clock amplitude is relatively low, the internal filter will filter off more

noise, yielding a better performance. If the theoretical upper limit is approached,

playability (e.g. black dot performance) will drop significantly. The decoder will only be able

to correct the biggest correctable burst error of 16 frames if f

clk(bit)ch

< f

clk(sys)

×

1.7 (Hz).

Taking this restriction on the decoder into account, the new range becomes:

f

clk(sys)

×

0.25 < f

clk(bit)ch

< f

clk(sys)

×

1.7 (Hz)

Digital HF PLL:

The digital PLL will recover the channel bit clock. The capture range of

the PLL itself is very limited. To overcome this difficulty, two capture aids are present.

When using automatic locking, the PLL will switch states based on the difference between

expected distance and actual distance between synchronization.

Three different PLL operating modes exist:

In-lock (normal operation): the PLL frequency matches the frequency of the channel

bits with an accuracy error of less than 1 %

Inner lock aid (capture aid 1): the PLL frequency matches the frequency of the

channel bits with an accuracy error of between 1 % and 10 %

Outer lock aid (capture aid 2): the PLL frequency is more than 10 % away from the

channel bit frequency

The operation of PLL in-lock (normal on-track situation) is explained below followed by

lock-detection and then the two capture aids.

PLL in-lock characteristics:

The PLL behavior during in-lock can best be explained in

the frequency domain. PLL operation is completely linear during in-lock situations. The

open-loop response of the PLL (bode diagram) is given in

Figure 17

.

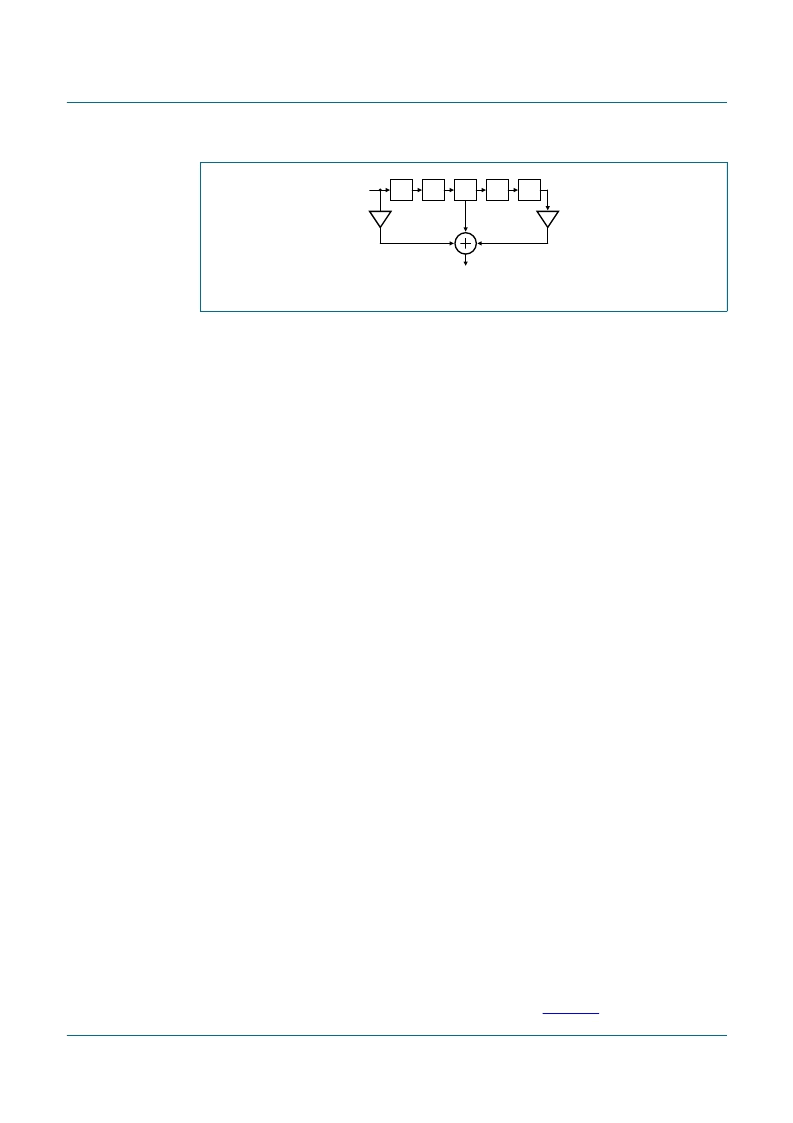

Fig 16. Equalizer block diagram

001aag320

α

1

α

1

D

D

D

D

D

in

out

+

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAF7846HL | One chip CD audio device with integrated MP3-WMA decoder |

| SAF7847HL | One chip CD audio device with integrated MP3-WMA decoder |

| SAF7849HL | One chip CD audio device with integrated MP3-WMA decoder |

| SB-015 | GMR Digital Sensor Evaluation Kit |

| SB10100F | ISOLATION SCHOTTKY BARRIER RECTIFIERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAF7843HL/M295,557 | 功能描述:音頻 DSP IC AUD DECODER RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| SAF7846HL/M210,557 | 功能描述:音頻 DSP 1 chip CD Audio Dev w/Integrated decoder RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| SAF7847HL/M201,557 | 功能描述:音頻 DSP 1 chip CD Audio Dev w/Integrated decoder RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| SAF7849HL/M245,557 | 功能描述:音頻 DSP IC AUD DECODER RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| SAF7849HL/M295,557 | 功能描述:音頻 DSP IC AUD DECODER RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。