- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372113 > SAA7128 (NXP Semiconductors N.V.) Digital video encoder PDF資料下載

參數(shù)資料

| 型號: | SAA7128 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Digital video encoder |

| 中文描述: | 數(shù)字視頻編碼器 |

| 文件頁數(shù): | 27/56頁 |

| 文件大小: | 192K |

| 代理商: | SAA7128 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

2000 Mar 08

27

Philips Semiconductors

Product specification

Digital video encoder

SAA7128H; SAA7129H

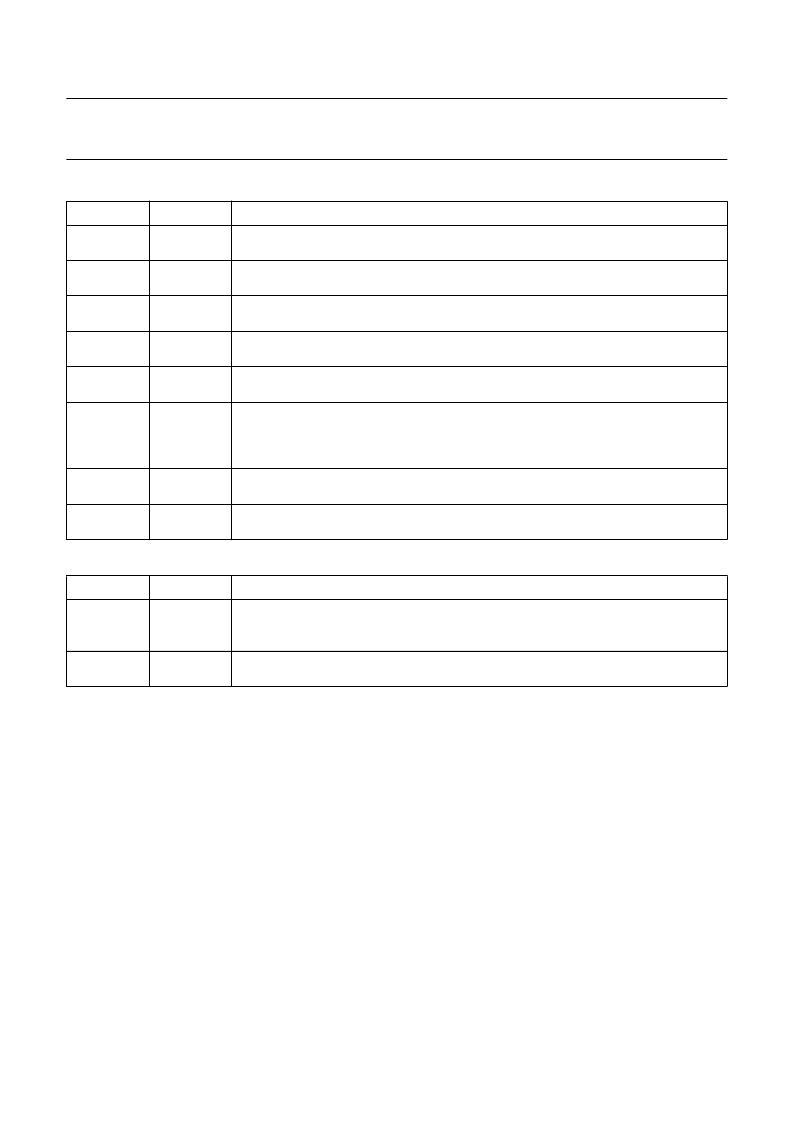

Table 42

Subaddress 61H

Table 43

Subaddress 62H

BIT

SYMBOL

DESCRIPTION

7

DOWNB

0 = DACs for R, G and B in normal operational mode

1 = DACs for R, G and B forced to lowest output voltage; default state after reset

0 = DACs for CVBS, Y and C in normal operational mode; default state after reset

1 = DACs for CVBS, Y and C forced to lowest output voltage

0 = PAL switch phase is nominal; default state after reset

1 = PAL switch phase is inverted compared to nominal if RTC is enabled (see Table 43).

0 = luminance gain for white

black 100 IRE; default state after reset

1 = luminance gain for white

black 92.5 IRE including 7.5 IRE set-up of black

0 = no SECAM encoding; default state after reset

1 = SECAM encoding activated; bit PAL has to be set to logic 0

0 = enlarged bandwidth for chrominance encoding (for overall transfer characteristic of

chrominance in baseband representation see Figs 8 and 9)

1 = standard bandwidth for chrominance encoding (for overall transfer characteristic of

chrominance in baseband representation see Figs 8 and 9); default state after reset

0 = NTSC encoding (non-alternating V component)

1 = PAL encoding (alternating V component); default state after reset

0 = 864 total pixel clocks per line; default state after reset

1 = 858 total pixel clocks per line

6

DOWNA

5

INPI

4

YGS

3

SECAM

2

SCBW

1

PAL

0

FISE

BIT

SYMBOL

DESCRIPTION

7

RTCE

0 = no real-time control of generated subcarrier frequency; default state after reset

1 = real-time control of generated subcarrier frequency through SAA7151B or

SAA7111; for timing see Fig.22

amplitude of colour burst; input representation in accordance with “ITU-R BT.601” see

Table 44

6 to 0

BSTA[6:0]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7128H | Digital video encoder |

| SAA7129 | Digital video encoder |

| SAA7129H | Digital video encoder |

| SAA7130 | PCI video broadcast decoder |

| SAA7134 | PCI audio and video broadcast decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7128A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital video encoder |

| SAA7128AH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital video encoder |

| SAA7128H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital video encoder |

| SAA7129 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital video encoder |

| SAA7129/DENC29A | 制造商:NXP Semiconductors 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。