- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372113 > SAA7114H (NXP SEMICONDUCTORS) PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler PDF資料下載

參數(shù)資料

| 型號: | SAA7114H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler |

| 中文描述: | COLOR SIGNAL DECODER, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT407-1, LQFP-100 |

| 文件頁數(shù): | 43/147頁 |

| 文件大?。?/td> | 759K |

| 代理商: | SAA7114H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁

2004 Mar 03

43

Philips Semiconductors

Product specification

PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC

comb filter, VBI data slicer and high performance scaler

SAA7114

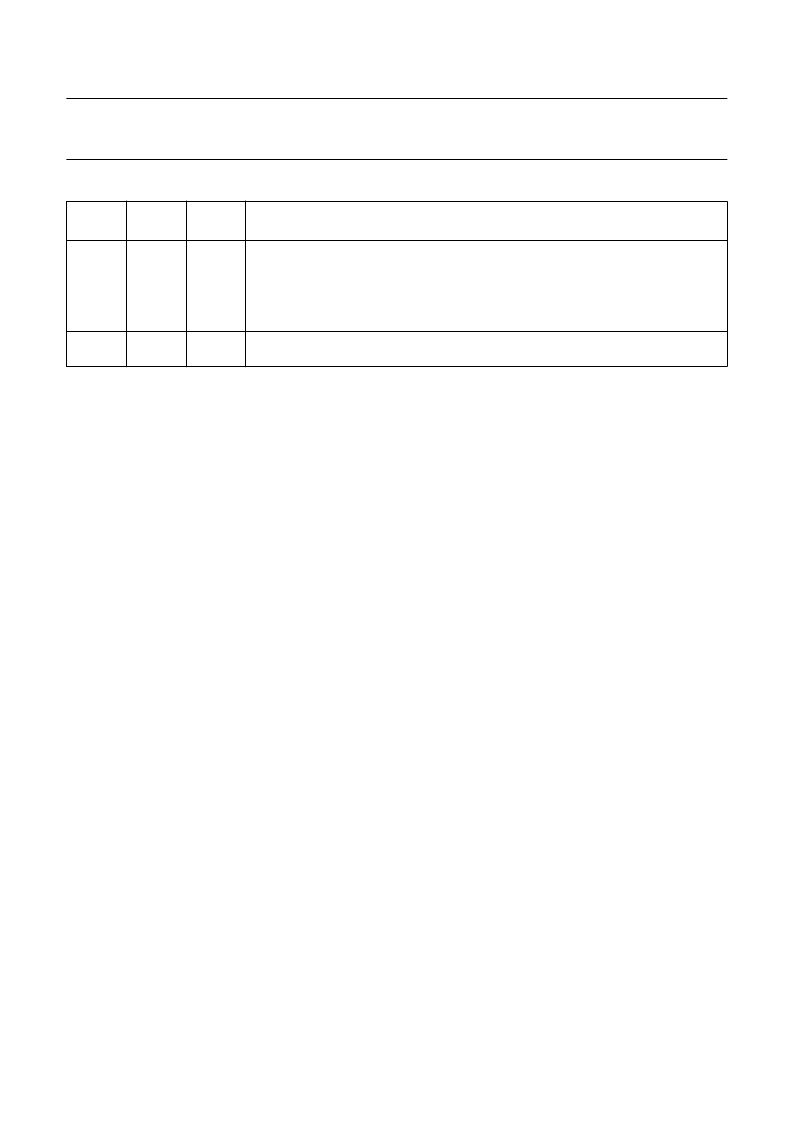

Table 9

Processing trigger and start

XDV1

92H[5]

XDV0

92H[4]

XDH

92H[2]

DESCRIPTION

Internal decoder

: The processing triggers at the falling edge of the V123 pulse

[see Figs 22 (50 Hz) and 23 (60 Hz)], and starts earliest with the rising edge of the

decoder HREF at line number:

4/7 (50/60 Hz, 1st field), respectively 3/6 (50/60 Hz, 2nd field) (decoder count)

2/5 (50/60 Hz, 1st field), respectively 2/5 (50/60 Hz, 2nd field) (decoder count)

External ITU 656 stream

: The processing starts earliest with SAV at line number 23

(50 Hz system), respectively line 20 (60 Hz system) (according to ITU 656 count)

0

0

0

1

0

0

0

0

0

8.3.1.2

Task handling

The task handler controls the switching between the two

programming register sets. It is controlled by

subaddresses 90H and C0H. A task is enabled via the

global control bits TEA[80H[4]] and TEB[80H[5]].

The handler is then triggered by events, which can be

defined for each register set.

In the event of a programming error the task handling and

the complete scaler can be reset to the initial states by

setting the software reset bit SWRST[88H[5]] to logic 0.

Especiallyiftheprogrammingregisters,relatedacquisition

windowandscalearereprogrammedwhileataskisactive,

a software reset

must

be performed after programming.

Contrary to the disabling/enabling of a task, which is

evaluated at the end of a running task, when SWRST is at

logic 0 it sets the internal state machines directly to their

idle states.

The start condition for the handler is defined by bits

STRC[1:0] 90H[1:0] and means: start immediately, wait for

next V-sync, next FID at logic 0 or next FID at logic 1. The

FID is evaluated, if the vertical and horizontal offsets are

reached.

When RPTSK[90H[2]] is at logic 1 the actual running task

is repeated (under the defined trigger conditions), before

handing control over to the alternate task.

To support field rate reduction, the handler is also enabled

to skip fields (bits FSKP[2:0] 90H[5:3]) before executing

the task. A TOGGLE flag is generated (used for the correct

output field processing), which changes state at the

beginning of a task, every time a task is activated;

examples are given in Section 8.3.1.3.

Remarks:

To activate a task the start condition must be

fulfilled and the acquisition window offsets must be

reached

.

For example, in case of ‘start immediately’, and two

regions are defined for one field, the offset of the lower

region must be greater than (offset + length) of the

upper region, if not, the actual counted H and V position

at the end of the upper task is beyond the programmed

offsets and the processing will ‘wait for next V’.

Basicallythetriggerconditionsarechecked,whena

task is activated

. It is important to realize, that they are

not checked while a task is inactive. So you can not

trigger to next logic 0 or logic 1 with overlapping offset

and active video ranges between the tasks (e.g. task A

STRC[2:0] = 2, YO[11:0] = 310 and task B

STRC[2:0] = 3, YO[11:0] = 310 results in output field

rate of

50

3

Hz).

After power-on or software reset (via

SWRST[88H[5]]) task B gets priority over task A

.

8.3.1.3

Output field processing

As a reference for the output field processing, two signals

are available for the back-end hardware.

These signals are the input field ID from the scaler source

and a TOGGLE flag, which shows that an active task is

used an odd (1, 3, 5...) or even (2, 4, 6...) number of times.

Using a single or both tasks and reducing the field or frame

rate with the task handling function, the TOGGLE

information can be used to reconstruct an interlaced

scaled picture at a reduced frame rate. The TOGGLE flag

isn’t synchronized to the input field detection, as it is only

dependent on the interpretation of this information by the

external hardware, whether the output of the scaler is

processed correctly; see Section 8.3.3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7114E | PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler |

| SAA7114 | PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC combfilter, VBI-data slicer and high performance scaler |

| SAA7115 | PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb Filter, High Performance Scaler, I2C Sliced Data Readback and SQ PIXEL OUTPUT |

| SAA7116 | Digital Video to PCI Interface |

| SAA7116H | Video Converter Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7114H/V2 | 制造商:NXP Semiconductors 功能描述:7114H/V2557 |

| SAA7114H/V2,518 | 功能描述:視頻 IC DIGITAL VIDEO DECODER W/COMB F RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7114H/V2,557 | 功能描述:視頻 IC DECODR W/FILTR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7114H/V2557 | 制造商:NXP Semiconductors 功能描述:VIDEO DECODER W/FILTER 100LQFP |

| SAA7114H_1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Video decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。