- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372110 > SAA5355 (NXP SEMICONDUCTORS) Single-chip colour CRT controller FTFROM PDF資料下載

參數(shù)資料

| 型號: | SAA5355 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顯示控制器 |

| 英文描述: | Single-chip colour CRT controller FTFROM |

| 中文描述: | 40 X 80 CHARACTERS CRT CHAR DSPL CTLR, PDIP40 |

| 文件頁數(shù): | 24/31頁 |

| 文件大小: | 335K |

| 代理商: | SAA5355 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

March 1986

24

Philips Semiconductors

Product specification

Single-chip colour CRT controller

(FTFROM)

SAA5355

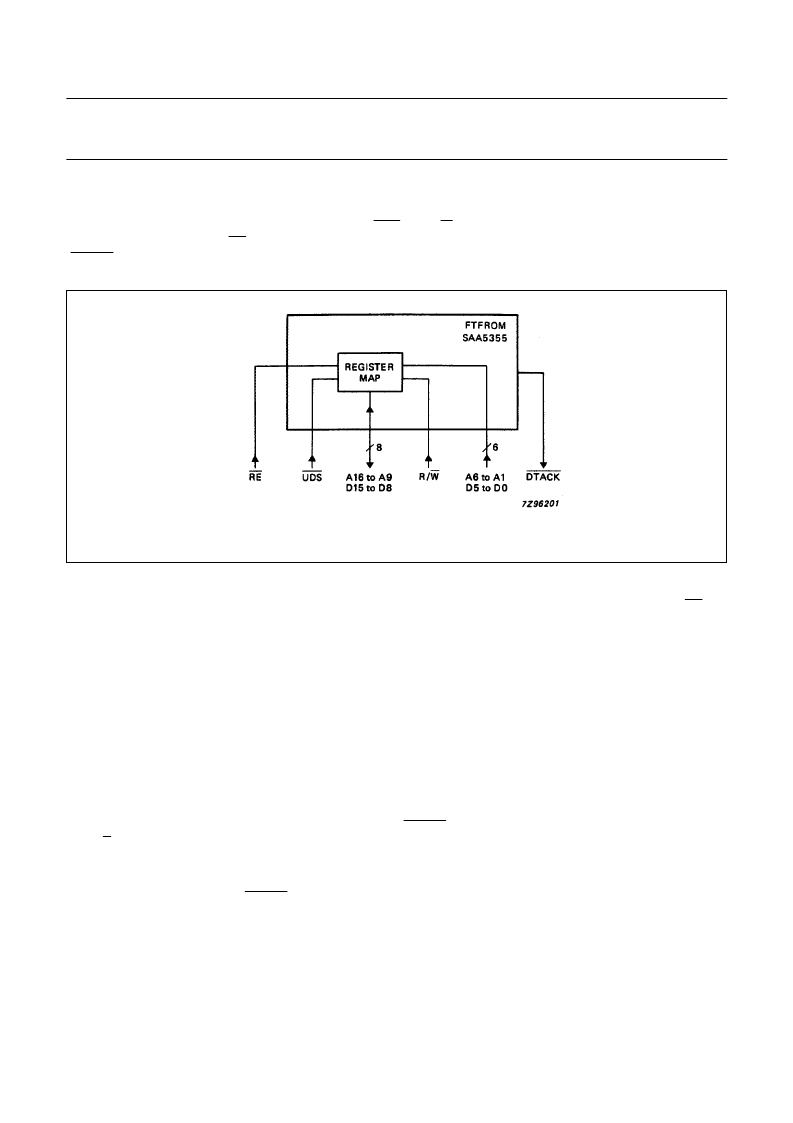

Microprocessor access to register map

FTFROM has a set of internal registers which, when memory-mapped, behave as an 8-bit wide RAM connected to the

upper part of the data bus (Fig.20). The control signals UDS and R/W are reversed to become inputs and the register

map is enabled by the signal RE. Addresses are input via the lower part of the bus. A data transfer acknowledge signal

(DTACK) indicates to the microprocessor that the data transfer is complete.

The main data and address paths used in a connected 68000 interface are shown in Fig.21. The outputs from the octal

latches (74LS373) are enabled only when the 68000 has made the bus available in response to a bus request (BR).

When the register map is accessed data is transferred via the upper part of the bus and the microprocessor’s low-order

address is passed to FTFROM via the octal buffers (74LS244). At the same time the bidirectional buffers (74LS245)

disable the signals from the low order data bus of the 68000.

The buffers ‘244 and ‘245 may be omitted in a 16-bit write-only configuration where the least-significant data byte is

interpreted by FTFROM as an address. Here it will generally be necessary for the microprocessor to hold a (readable)

‘master copy’ of FTFROM’s scroll map contents at a location in its main memory.

8-bit microprocessors

Although the control bus is optimised for the SCN68000 16-bit microprocessor unit, FTFROM will operate with a number

of widely differing industry-standard 8, 16 or more-bit microprocessors or microcontrollers (e.g. SCN68008, MAB8051).

The interfacing of 8-bit microprocessors to the 16-bit wide display memory is made simple by FTFROM’s on-chip

link-through buffer which provides the microprocessor with bidirectional access to the lower (odd) half of the memory.

The link-through buffer is enabled by the buffer-enable signal BUFEN, and the send/receive direction is controlled by the

signal S/R.

The main data and address paths used in a connected 8-bit microprocessor system are shown in Fig.22. The interface

is similar to that of the 16-bit system but here the display memory does not receive A0 as an address, rather A0 is used

as the major enabling signal for BUFEN (enables when HIGH).

Fig.20 Microprocessor access to register map.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA5360 | Multi page intelligent teletext decoder |

| SAA5360HL | Multi page intelligent teletext decoder |

| SAA5361 | Multi page intelligent teletext decoder |

| SAA5361HL | Multi page intelligent teletext decoder |

| SAA5491H | DPST MINIATURE POWER RELAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA5360 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi page intelligent teletext decoder |

| SAA5360HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi page intelligent teletext decoder |

| SAA5361 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi page intelligent teletext decoder |

| SAA5361HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi page intelligent teletext decoder |

| SAA5361HL/M1/1651 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SAA5361HL/M1/1651 TSG0537/M1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。