- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139C_PLUS RTL8139C_Plus Specification PDF資料下載

參數(shù)資料

| 型號: | RTL8139C_PLUS |

| 英文描述: | RTL8139C_Plus Specification |

| 中文描述: | RTL8139C_Plus規(guī)范 |

| 文件頁數(shù): | 32/58頁 |

| 文件大?。?/td> | 616K |

| 代理商: | RTL8139C_PLUS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

32

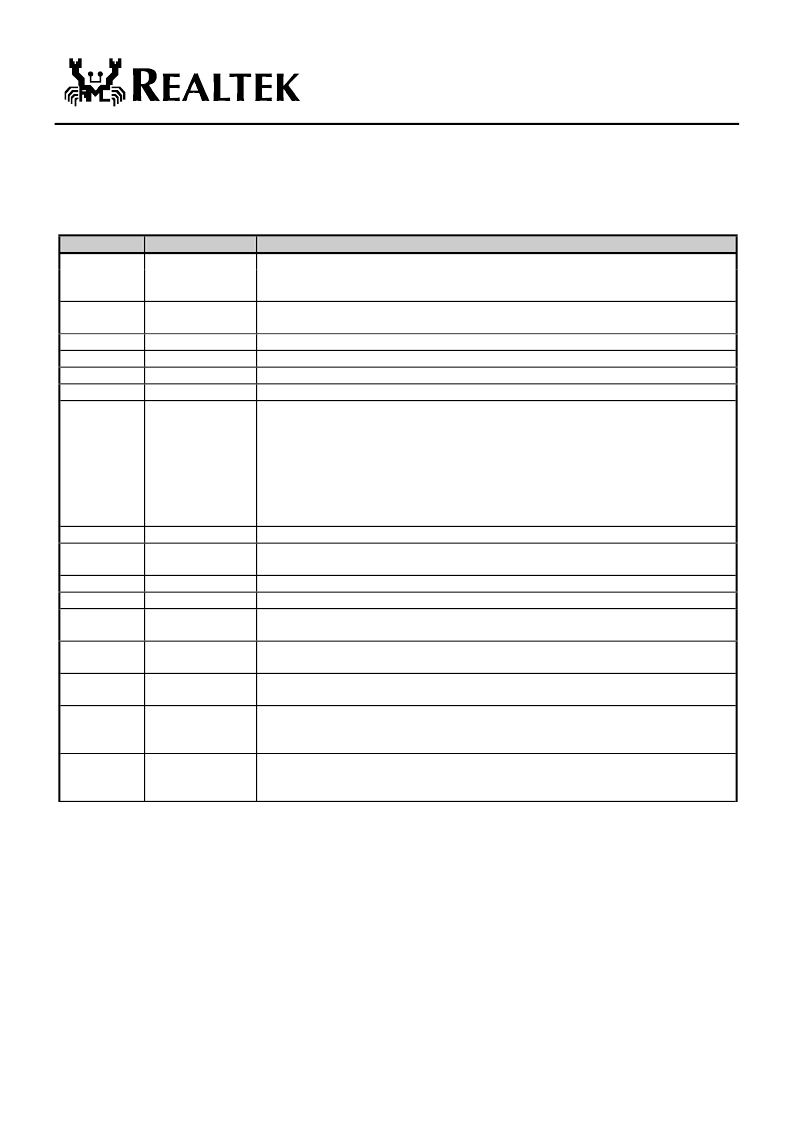

6. EEPROM (93C46) Contents

The 93C46 is a 1K-bit EEPROM. Although it is actually addressed by words, its contents are listed below by bytes for

convenience. The RTL8100B(L) performs a series of EEPROM read operations from the 93C46 addresses 00H to 31H.

It is suggested to obtain Realtek approval before changing the default settings of the EEPROM.

Bytes

00h

01h

Contents

29h

81h

Description

These 2 bytes contain the ID code word for the RTL8100B(L). The RTL8100B(L) will load

the contents of the EEPROM into the corresponding location if the ID word (8129h) is right,

otherwise, the RTL8100B(L) will not proceed with the EEPROM autoload process.

Reserved. The RTL8100B(L) no longer supports autoload of Vender ID and Device ID.

The default values of VID and DID are hex 10EC and 8139, respectively.

PCI Subsystem Vendor ID, PCI configuration space offset 2Ch-2Dh.

PCI Subsystem ID, PCI configuration space offset 2Eh-2Fh.

PCI Minimum Grant Timer, PCI configuration space offset 3Eh.

PCI Maximum Latency Timer, PCI configuration space offset 3Fh.

Bits 7-6 map to bits 7-6 of the Media Status register (MSR); Bits 5, 4, 0 map to bits 13,

12, 8 of the Basic Mode Control register (BMCR); Bits 3-2 are reserved. If the network

speed is set to Auto-Detect mode (i.e. Nway mode), then Bit 1=0 means the local

RTL8100B(L) supports flow control (IEEE 802.3x). In this case, Bit 10=1 in the

Auto-negotiation Advertisement Register (offset 66h-67h), and Bit 1=1 means the local

RTL8100B(L) does not support flow control. In this case, Bit 10=0 in Auto-negotiation

Advertisement. This is because there are Nway switch hubs which keep sending flow

control pause packets for no reason, if the link partner supports Nway flow control.

RTL8100B(L) Configuration register 3, operational register offset 59H.

After auto-load command or hardware reset, the RTL8100B(L) loads the Ethernet ID to

IDR0-IDR5 of RTL8100B(L)'s I/O registers.

RTL8100B(L) Configuration register 0, operational registers offset 51h.

RTL8100B(L) Configuration register 1, operational registers offset 52h.

Reserved. Do not change this field without Realtek approval.

Power Management Capabilities. PCI configuration space address 52h and 53h.

Reserved. Do not change this field without Realtek approval.

Power Management Control/Status. PCI configuration space address 55h.

Reserved. Do not change this field without Realtek approval.

RTL8100B(L) Configuration register 4, operational registers offset 5Ah.

PHY1_PARM_U Reserved. Do not change this field without Realtek approval.

PHY Parameter 1-U for RTL8100B(L). Operational registers of the RTL8100B(L) are

from 78h to 7Bh.

PHY2_PARM_U Reserved. Do not change this field without Realtek approval.

PHY Parameter 2-U for RTL8100B(L). Operational register of the RTL8100B(L) is

80h.

02h-05h

-

06h-07h

08h-09h

0Ah

0Bh

0Ch

SVID

SMID

MNGNT

MXLAT

MSRBMCR

0Dh

0Eh-13h

CONFIG3

Ethernet ID

14h

15h

CONFIG0

CONFIG1

PMC

16h-17h

18h

PMCSR

19h

CONFIG4

1Ah-1Dh

1Eh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139D(L) | RTL8139D(L) Specification |

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139D(L) Specification |

| RTL8139D-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。