- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139C_PLUS RTL8139C_Plus Specification PDF資料下載

參數(shù)資料

| 型號: | RTL8139C_PLUS |

| 英文描述: | RTL8139C_Plus Specification |

| 中文描述: | RTL8139C_Plus規(guī)范 |

| 文件頁數(shù): | 10/58頁 |

| 文件大?。?/td> | 616K |

| 代理商: | RTL8139C_PLUS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

10

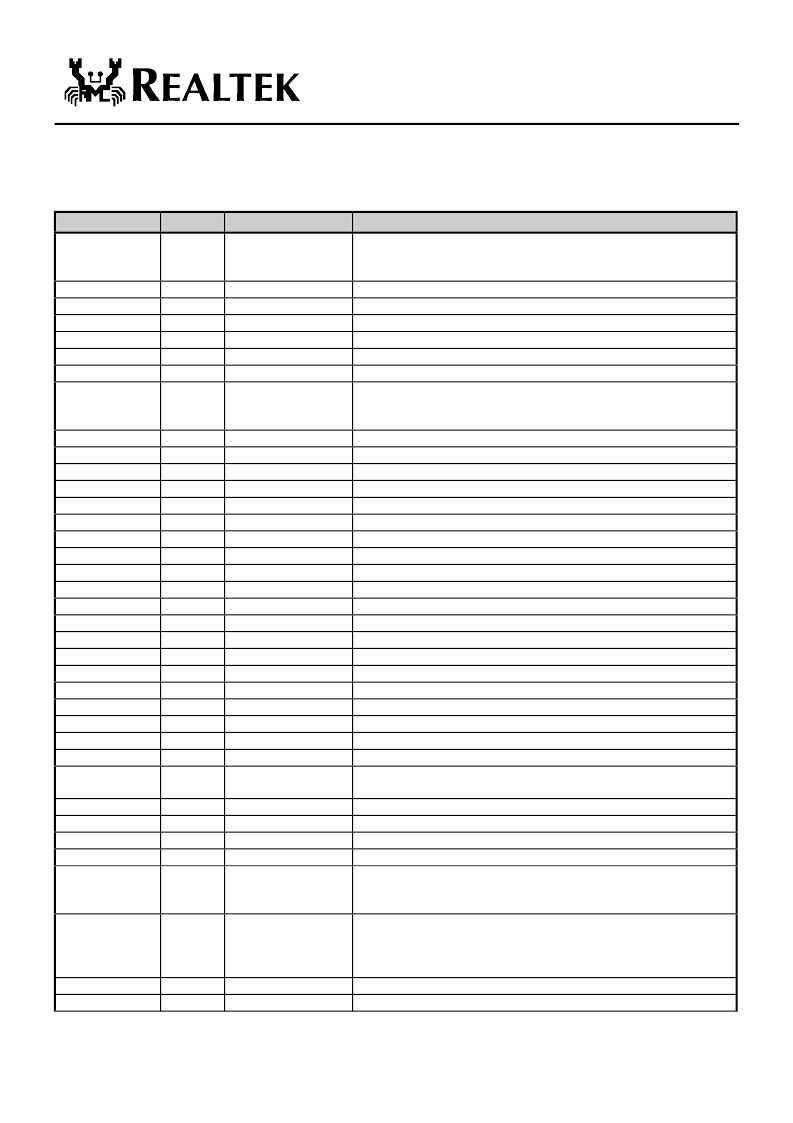

5. Register Descriptions

The RTL8100B(L) provides the following set of operational registers mapped into PCI memory space or I/O space.

Offset

R/W

Tag

0000h

R/W

IDR0

ID Register 0:

ID registers 0-5 are only permitted to read/write by

4-byte access. Read access can be byte, word, or double word access.

The initial value is autoloaded from the EEPROM EthernetID field.

0001h

R/W

IDR1

ID Register 1

0002h

R/W

IDR2

ID Register 2

0003h

R/W

IDR3

ID Register 3

0004h

R/W

IDR4

ID Register 4

0005h

R/W

IDR5

ID Register 5

0006h-0007h

-

-

Reserved

0008h

R/W

MAR0

Multicast Register 0:

The MAR register 0-7 are only permitted to

read/write by 4-byte access. Read access can be byte, word, or double

word access. Driver is responsible for initializing these registers.

0009h

R/W

MAR1

Multicast Register 1

000Ah

R/W

MAR2

Multicast Register 2

000Bh

R/W

MAR3

Multicast Register 3

000Ch

R/W

MAR4

Multicast Register 4

000Dh

R/W

MAR5

Multicast Register 5

000Eh

R/W

MAR6

Multicast Register 6

000Fh

R/W

MAR7

Multicast Register 7

0010h-0013h

R/W

TSD0

Transmit Status of Descriptor 0

0014h-0017h

R/W

TSD1

Transmit Status of Descriptor 1

0018h-001Bh

R/W

TSD2

Transmit Status of Descriptor 2

001Ch-001Fh

R/W

TSD3

Transmit Status of Descriptor 3

0020h-0023h

R/W

TSAD0

Transmit Start Address of Descriptor0

0024h-0027h

R/W

TSAD1

Transmit Start Address of Descriptor1

0028h-002Bh

R/W

TSAD2

Transmit Start Address of Descriptor2

002Ch-002Fh

R/W

TSAD3

Transmit Start Address of Descriptor3

0030h-0033h

R/W

RBSTART

Receive (Rx) Buffer Start Address

0034h-0035h

R

ERBCR

Early Receive (Rx) Byte Count Register

0036h

R

ERSR

Early Rx Status Register

0037h

R/W

CR

Command Register

0038h-0039h

R/W

CAPR

Current Address of Packet Read

003Ah-003Bh

R

CBR

Current Buffer Address:

The initial value is 0000h. It reflects total

received byte-count in the Rx buffer.

003Ch-003Dh

R/W

IMR

Interrupt Mask Register

003Eh-003Fh

R/W

ISR

Interrupt Status Register

0040h-0043h

R/W

TCR

Transmit (Tx) Configuration Register

0044h-0047h

R/W

RCR

Receive (Rx) Configuration Register

0048h-004Bh

R/W

TCTR

Timer CounT Register:

This register contains a 32-bit

general-purpose timer. Writing any value to this 32-bit register will

reset the original timer and begin to count from zero.

004Ch-004Fh

R/W

MPC

Missed Packet Counter:

Indicates the number of packets discarded

due to Rx FIFO overflow. It is a 24-bit counter. After s/w reset, MPC

is cleared. Only the lower 3 bytes are valid.

When any value is written, MPC will be reset also.

0050h

R/W

9346CR

93C46 Command Register

0051h

R/W

CONFIG0

Configuration Register 0

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139D(L) | RTL8139D(L) Specification |

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139D(L) Specification |

| RTL8139D-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。