- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139C_PLUS RTL8139C_Plus Specification PDF資料下載

參數(shù)資料

| 型號(hào): | RTL8139C_PLUS |

| 英文描述: | RTL8139C_Plus Specification |

| 中文描述: | RTL8139C_Plus規(guī)范 |

| 文件頁(yè)數(shù): | 14/58頁(yè) |

| 文件大小: | 616K |

| 代理商: | RTL8139C_PLUS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

RTL8100B(L)

2001-11-9

Rev.1.41

14

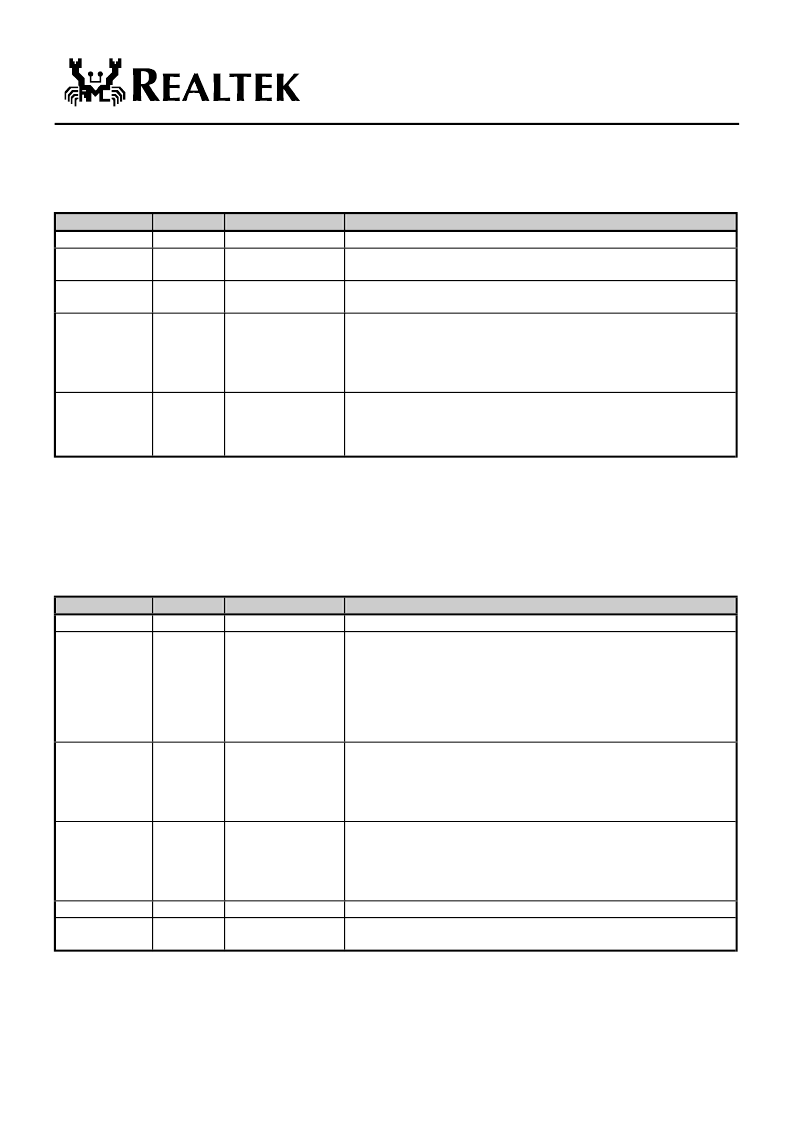

5.3 ERSR: Early Rx Status Register

(Offset 0036h, R)

Bit

7-4

3

R/W

-

R

Symbol

-

ERGood

Description

Reserved

Early Rx Good packet:

This bit is set whenever a packet is completely

received and the packet is good. Writing a 1 to this bit will clear it.

Early Rx Bad packet:

This bit is set whenever a packet is completely

received and the packet is bad. Writing a 1 to this bit will clear it.

Early Rx OverWrite:

This bit is set when the RTL8100B(L)'s local

address pointer is equal to CAPR. In the early mode, this is different

from buffer overflow. It happens that the RTL8100B(L) detected an Rx

error and wanted to fill another packet data from the beginning address

of that error packet. Writing a 1 to this bit will clear it.

Early Rx OK:

The power-on value is 0. It is set when the Rx byte count

of the arriving packet exceeds the Rx threshold. After the whole packet

is received, the RTL8100B(L) will set ROK or RER in ISR and clear

this bit simultaneously. Setting this bit will invoke a ROK interrupt.

2

R

ERBad

1

R

EROVW

0

R

EROK

5.4 Command Register

(Offset 0037h, R/W)

This register is used for issuing commands to the RTL8100B(L). These commands are issued by setting the corresponding bits for the

function. A global software reset along with individual reset and enable/disable for transmitter and receiver are provided here.

Bit

7-5

4

R/W

-

R/W

Symbol

-

RST

Description

Reserved

Reset:

Setting to 1 forces the RTL8100B(L) to a software reset state

which disables the transmitter and receiver, reinitializes the FIFOs,

resets the system buffer pointer to the initial value (Tx buffer is at

TSAD0, Rx buffer is empty). The values of IDR0-5 and MAR0-7 and

PCI configuration space will have no changes. This bit is 1 during the

reset operation, and is cleared to 0 by the RTL8100B(L) when the reset

operation is complete.

Receiver Enable:

When set to 1, and the receive state machine is idle,

the receive machine becomes active. This bit will read back as a 1

whenever the receive state machine is active. After initial power-up,

software must insure that the receiver has completely reset before

setting this bit. This bit will be reset after PCI reset deassertion.

Transmitter Enable:

When set to 1, and the transmit state machine is

idle, then the transmit state machine becomes active. This bit will read

back as a 1 whenever the transmit state machine is active. After initial

power-up, software must insure that the transmitter has completely reset

before setting this bit. This bit will be reset after PCI reset deassertion.

Reserved

Buffer Empty:

Rx Buffer Empty. There is no packet stored in the Rx

buffer ring.

3

R/W

RE

2

R/W

TE

1

0

-

R

-

BUFE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139D(L) | RTL8139D(L) Specification |

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139D(L) Specification |

| RTL8139D-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。