- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376249 > PSD312-15JI (意法半導(dǎo)體) Low Cost Field Programmable Microcontroller Peripherals PDF資料下載

參數(shù)資料

| 型號: | PSD312-15JI |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Low Cost Field Programmable Microcontroller Peripherals |

| 中文描述: | 低成本現(xiàn)場可編程微控制器外圍設(shè)備 |

| 文件頁數(shù): | 32/85頁 |

| 文件大?。?/td> | 691K |

| 代理商: | PSD312-15JI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

PSD3XX Famly

29

14.0

System

Applications

(cont.)

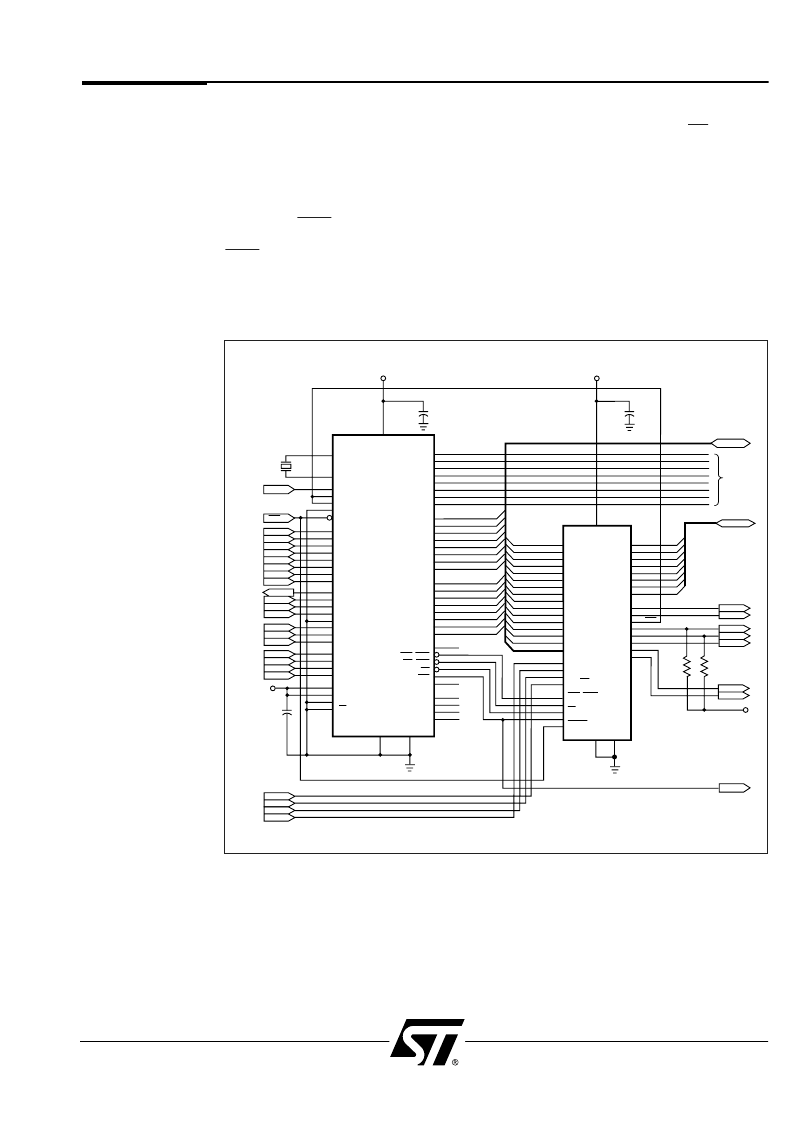

In Figure 13, the PSD3XX is configured to work directly with Intel’s 80C196KB

microcontroller, which is a 16-bit address/16-bit data bus processor. The Address and data

lines multiplexed. The PSD3XX is configured to use PC0, PC1, PC2, and A19/CSI as logic

inputs. These signals are independent of the ALE pulse (latch-transparent). They are used

as four general-purpose inputs that take part in the PAD equations.

Port A is configured to work in Track Mode, in which (for certain conditions) PA0–PA7 tracks

lines AD0/A0–AD7/A7. Port B is configured to generate CS0–CS7. In this example, PB2

serves as a WAIT signal that slows down the 80C196KB during the access of external

peripherals. These 8-bit wide peripherals are connected to the shared bus of Port A. The

WAIT signal also drives the buswidth input of the microcontroller, so that every external

peripheral cycle becomes an 8-bit data bus cycle. PB3 and PB4 are open-drain output

signals; thus, they are pulled up externally.

67

68

36

NMI

RxD

TxD

+5V

RST

66

XTAL1

AD[0..15]

AD[0..15]

XTAL2

3

43

64

14

16

NMI

READY

BUSWIDTH

CDE

RESET

6

5

7

4

11

10

8

9

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

18

17

15

44

42

39

33

38

P2.0/TXD

P2.1/RXD

P2.3/T2CLK

P2.4/T2RST

P2.5/PWM

P2.7/T2 CAPTR

AD0/A0

AD1/A1

AD2/A2

AD4/A4

AD5/A5

AD6/A6

AD8/A8

AD9/A9

AD10/A10

AD12/A12

AD13/A13

AD14/A14

21

20

19

18

17

16

15

14

11

10

9

8

7

6

5

4

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

AD0/A0

AD1/A1

AD2/A2

AD3/A3

AD4/A4

AD5/A5

AD6/A6

AD7/A7

AD8/A8

AD9/A9

AD10/A10

AD11/A11

AD12/A12

AD13/A13

AD14/A14

AD15/A15

AD0/A0

AD1/A1

AD2/A2

AD3/A3

AD4/A4

AD5/A5

AD6/A6

AD7/A7

AD8/A8

AD9/A9

AD10/A10

AD11/A11

AD12/A12

AD13/A13

AD14/A14

AD15/A15

23

24

25

26

27

28

29

30

31

32

33

35

36

37

38

39

40

41

42

43

1

2

22

13

3

PC0

PC1

PC2

A19/CSI

BHE/PSEN

WR/V

PP

RD

ALE

RESET

24

25

26

27

HSI.0

HSI.1

HSI.2/HSO.4

HSI.3/HSO.5

13

37

12

2

VREF

VPP

ANGND

EA

19

20

21

22

23

30

31

32

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

65

41

40

61

62

63

28

29

34

35

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P3.0/AD0

P3.1/AD1

P3.2/AD2

P3.3/AD3

P3.4/AD4

P3.5/AD5

P3.6/AD6

P3.7/AD7

P4.0/AD8

P4.1/AD9

P4.2/AD10

P4.3/AD11

P4.4/AD12

P4.5/AD13

P4.6/AD14

P4.7/AD15

CLKOUT

BHE/WRH

WR/WRL

RD

ALE/ADV

INST

HSO.0

HSO.1

HSO.2

HSO.3

VSS

0.1μF

0.1μF

FOUR

GENERAL

PURPOSE

INPUTS

GND GND

12

34

+5V

+5V

+5V

4.7K

4.7K

0.1μF

ALE

WAIT

SHARED

BUS

PORT 1

I/O PINS

44

VCC

VCC

VSS

ADDRESS/DATA

MULTIPLEXED BUS

80C196KB

PSD3XX

Figure 13. PSD3XX Interface With Intel’s 80C196KB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD312-15JM | Low Cost Field Programmable Microcontroller Peripherals |

| PSD312R-15J | Low Cost Field Programmable Microcontroller Peripherals |

| PSD312R-15JI | Low Cost Field Programmable Microcontroller Peripherals |

| PSD312R-15JM | Low Cost Field Programmable Microcontroller Peripherals |

| PSD312R-20J | Low Cost Field Programmable Microcontroller Peripherals |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD312-15JM | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD312-15LI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD312-15LM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD312-15Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD312-15QI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。