- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367933 > PH28F256L18B85 (INTEL CORP) StrataFlash Wireless Memory PDF資料下載

參數(shù)資料

| 型號(hào): | PH28F256L18B85 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | StrataFlash Wireless Memory |

| 中文描述: | 16M X 16 FLASH 1.8V PROM, 85 ns, PBGA79 |

| 封裝: | 0.75 MM PITCH, LEAD FREE, VFBGA-79 |

| 文件頁數(shù): | 88/106頁 |

| 文件大?。?/td> | 1272K |

| 代理商: | PH28F256L18B85 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁當(dāng)前第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

Intel StrataFlash Wireless Memory (L18)

April 2005

88

Intel StrataFlash Wireless Memory (L18)

Order Number: 251902, Revision: 009

Datasheet

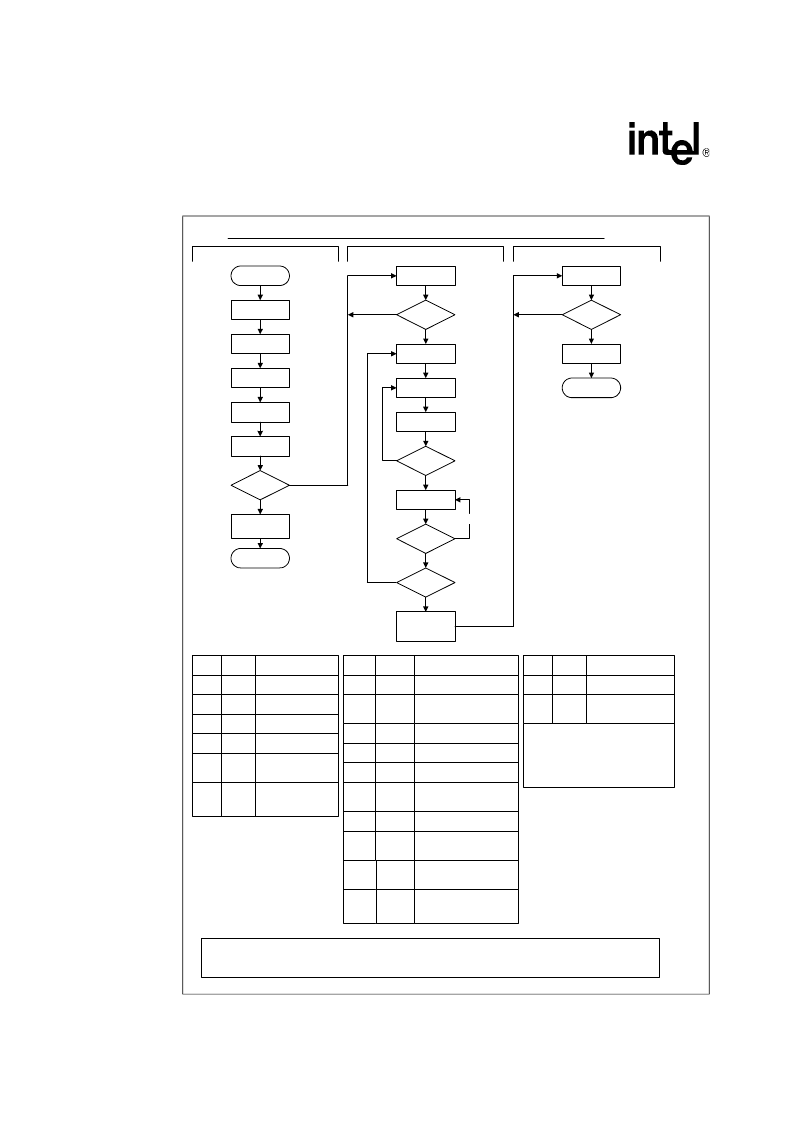

Figure 42.

Buffered EFP Flowchart

Write Data @ 1

ST

Word Address

Last

Data

Write 0xFFFF,

Address Not within

Current Block

Program

Done

Read Status Reg.

Y

No (SR[7]=0)

Full Status Check

Procedure

Program

Complete

Read Status Reg.

BEFP

Exited

Yes (SR[7]=1)

Start

Write 0x80 @

1

ST

Word Address

V

applied,

Block unlocked

Write 0xD0 @

1

ST

WordAddress

BEFP Setup

Done

Read Status Reg.

Exit

N

Program & Verify Phase

Exit Phase

Setup Phase

BUFFERED ENHANCED FACTORY PROGRAMMING (Buffered-EFP) PROCEDURE

X = 32

Initialize Count:

X = 0

Increment Count:

X = X+1

Y

NOTES:

1. First-word address to be programmed within the target blockmust be aligned on a write-buffer boundary.

2. Write-buffer contents are programmed sequentially to the flash array starting at the first word address;

WSM internally increments addressing.

N

Check V

, Lock

Errors (SR[3,1])

Yes (SR[7]=0)

Comments

Bus

State

Operation

BEFP setup delay

DReady

Read Status Reg.

No (SR[0]=1)

Repeat for subsequent blocks;

After BEFP exit, a full Status Register check can

determine if any program error occurred;

See full Status Register check procedure in the

Word Program flowchart.

Write 0xFF to enter Read Array state.

Check SR[7]:

0 = Exit Not Completed

1 = Exit Completed

CStatus

Read

Status

Data = Status Reg. Data

BEFP Exit

Standby

If SR[7] is set, check:

SR[3] set = V

Error

SR[1] set = Locked Block

Error

Condition

Check

Standby

Check SR[7]:

0 = BEFP Ready

BEFP

Setup

Standby

Data = Status Reg. Data

ST

Word Addr

Status

Read

Data = 0xD0 @

1

Address

ST

Word

BEFP

Confirm

Write

ST

Word

Data = 0x80 @ 1

BEFP

(Write

V

PPH

applied to VPP

Block

Write

BEFP Setup

Bus

State

Comments

Operation

No (SR[0]=1)

Yes (SR[0]=0)

No (SR[7]=1)

Yes (SR[0]=0)

BEFP Program & Verify

Comments

Bus State Operation

Write

(Note 2)

Load

Buffer

Standby

InCount

Standby

Initialize

Count

Data = Data to Program

Address = 1

ST

Word Addr.

X = X+1

X = 0

Standby

Buffer

Full

X = 32

Yes = Read SR[0]

Read

Standby

Status

DReady

Data = Status Register Data

ST

Word Addr.

Check SR[0]:

0 = Ready for Data

1 = Not Ready for Data

Read

Standby

Standby

Write

Status

Register

Program

Done

Last

Data

Exit Prog &

Verify Phase

Data = Status Reg. data

Address = 1

ST

Word Addr.

Check SR[0]:

0 = Program Done

1 = Program in Progress

No = Fill buffer again

Yes = Exit

Data = 0xFFFF @ address not in

current block

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PH28F256L18T85 | StrataFlash Wireless Memory |

| PH28F640L18B85 | StrataFlash Wireless Memory |

| PH28F640L18T85 | StrataFlash Wireless Memory |

| PH2907A | PNP switching transistor |

| PH2907 | PNP switching transistor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PH28F256L18B85A | 制造商:Micron Technology Inc 功能描述:MM#875138FLASH 28F256L18B 85 VF-PBGA79 S |

| PH28F256L18T85 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F320C3TD70A | 制造商:Micron Technology Inc 功能描述:Flash Mem Parallel 3V/3.3V 32M-Bit 2M x 16 70ns 48-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:MM#869664FLASH 28F320C3TD 70 VF-PBGA47 E |

| PH28F320W18BE60A | 制造商:Micron Technology Inc 功能描述:IC FLASH 32MBIT 60NS VFBGA |

| PH28F320W18BE60B | 制造商:Micron Technology Inc 功能描述:32MB, CRYSTAL .75 VFBGA 1.8 LF - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。