- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367908 > pentium III (Intel Corp.) pentium III Processor for the PGA370 Socket at 500MHz to 933MHz(工作頻率500到933兆赫茲活動帶PGA370插孔奔III處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium III |

| 廠商: | Intel Corp. |

| 英文描述: | pentium III Processor for the PGA370 Socket at 500MHz to 933MHz(工作頻率500到933兆赫茲活動帶PGA370插孔奔III處理器) |

| 中文描述: | 奔騰III處理器在500MHz到933MHz的(工作頻率500到933兆赫茲活動帶PGA370插孔奔三處理器的PGA370插座) |

| 文件頁數(shù): | 21/78頁 |

| 文件大小: | 610K |

| 代理商: | PENTIUM III |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

Datasheet

21

Pentium

III Processor for the PGA370 Socket at 500 MHz to 933 MHz

2.8.2

System Bus Frequency Select Signals (BSEL[1:0])

These signals are used to select the system bus frequency.

Table 2.9

defines the possible

combinations of the signals and the frequency associated with each combination. The frequency is

determined by the processor(s), chipset, and clock synthesizer. All system bus agents must operate

at the same frequency.

The Pentium

III

processor for the PGA370 socket operates at 100 MHz

or 133 MHz system bus frequency; 66 MHz system bus operation is not supported

. Individual

processors will only operate at their specified front side bus (FSB) frequency, either 100 MHz or

133 MHz, not both.

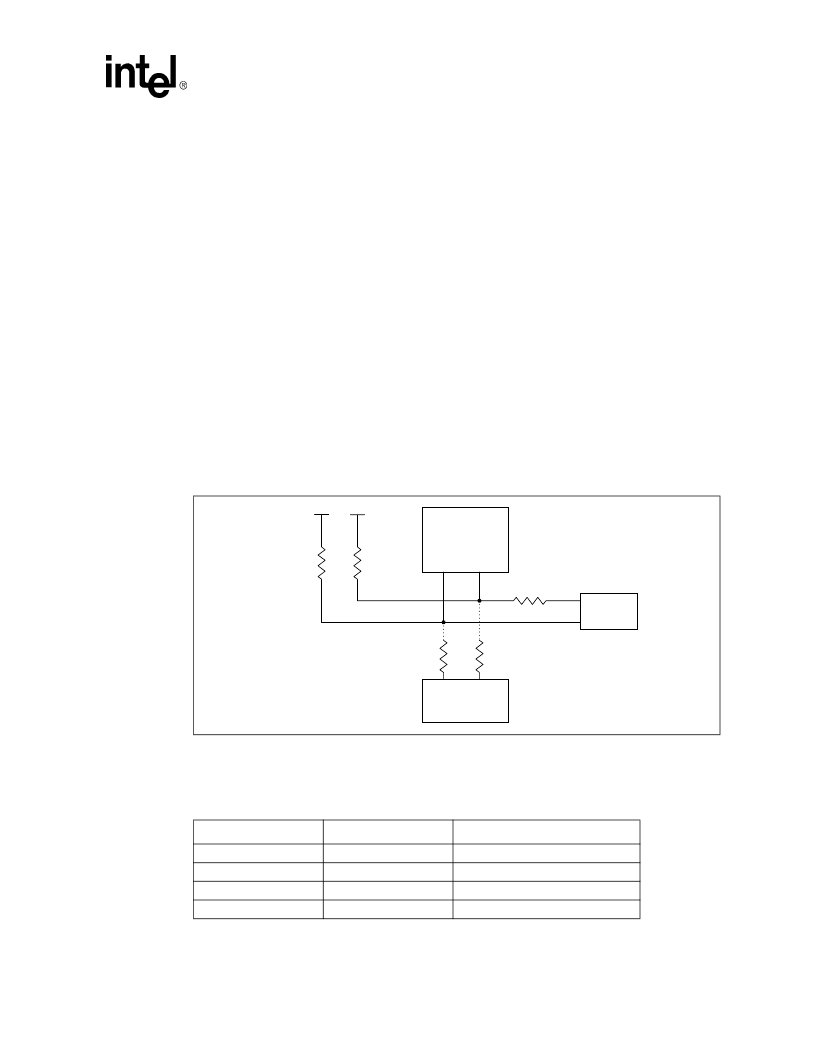

On motherboards that support operation at either 100 MHz or 133 MHz, the BSEL1 signal must be

pulled up to a logic high by a resistor located on the motherboard and provided as a frequency

selection signal to the clock driver/synthesizer. This signal can also be incorporated into RESET#

logic on the motherboard if only 133 MHz operation is supported (thus forcing the RESET# signal

to remain active as long as the BSEL1 signal is low.

The BSEL0 signal will float from the processor and should be pulled up to a logic high by a resistor

located on the motherboard. The BSEL0 signal can be incorporated into RESET# logic on the

motherboard if 66 MHz operation is unsupported, as demonstrated in

Figure 6

. Refer to the

appropriate clock synthesizer design guidelines and platform design guide for more details on the

bus frequency select signals.

In a 2-way MP system design, these BSEL[1:0] signals must connect the pins of both processors.

NOTES:

1. Some clock drivers may require a series resistor on their BSEL1 input.

2. Some chipsets may connect to the BSEL[1:0] signals and require a series resistor. See the appropriate

platform design guide for implementation details.

Figure 6. BSEL[1:0] Example for a 100/133 MHz or 100 MHz Only System Design

Processor

BSEL0

BSEL1

Chipset

Clock Driver

1 K

1 K

3.3V

3.3V

10 K

Note 1

10 K

Note 2

10 K

Note 2

Table 4. Frequency Select Truth Table for BSEL[1:0]

BSEL1

BSEL0

Frequency

0

0

66 MHz (unsupported)

0

1

100 MHz

1

0

Reserved

1

1

133 MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium II | pentium II processor With On-die Cache Mobile Module Connector 1 (MMC-1)(帶緩存和連接器1的奔II處理器) |

| PERICOMPI7C8150 | 2-Port PCI-to-PCI Bridge |

| PESDXL2BT | Low capacitance double bidirectional ESD protection diodes in SOT23 |

| PESDXL2UM | LJT 23C 21#20 2#16 PIN RECP |

| PETAM1270BK300R | BRAID SLEEVING 300M |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。