- 您現在的位置:買賣IC網 > PDF目錄369950 > PCI2050GHK BUS CONTROLLER PDF資料下載

參數資料

| 型號: | PCI2050GHK |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 總線控制器 |

| 文件頁數: | 3/17頁 |

| 文件大小: | 220K |

| 代理商: | PCI2050GHK |

PCI2050A

PCI-to-PCI BRIDGE

SCPS067

–

MAY 2001

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

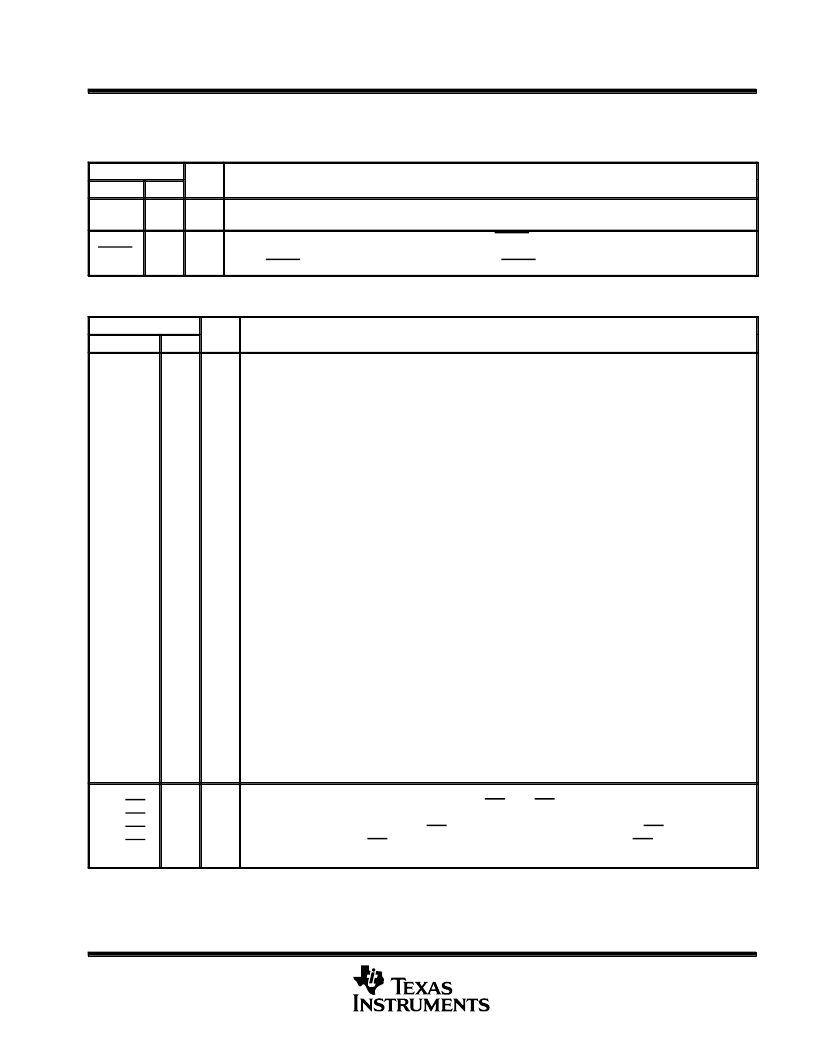

Terminal Functions

primary PCI system terminals

TERMINAL

NAME

I/O

DESCRIPTION

NO.

P_CLK

45

I

Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All primary PCI signals

are sampled at rising edge of P_CLK.

P_RST

43

I

PCI reset. When the primary PCI bus reset is asserted, P_RST causes the bridge to put all output buffers in a

high-impedance state and reset all internal registers. When asserted, the device is completely nonfunctional.

During P_RST, the secondary interface is driven low. After P_RST is deasserted, the bridge is in its default state.

primary PCI address and data terminals

TERMINAL

NAME

I/O

DESCRIPTION

NO.

P_AD31

P_AD30

P_AD29

P_AD28

P_AD27

P_AD26

P_AD25

P_AD24

P_AD23

P_AD22

P_AD21

P_AD20

P_AD19

P_AD18

P_AD17

P_AD16

P_AD15

P_AD14

P_AD13

P_AD12

P_AD11

P_AD10

P_AD9

P_AD8

P_AD7

P_AD6

P_AD5

P_AD4

P_AD3

P_AD2

P_AD1

P_AD0

49

50

55

57

58

60

61

63

67

68

70

71

73

74

76

77

93

95

96

98

99

101

107

109

112

113

115

116

118

119

121

122

I/O

Primary address/data bus. These signals make up the multiplexed PCI address and data bus on the primary

interface. During the address phase of a primary bus PCI cycle, P_AD31

–

P_AD0 contain a 32-bit address

or other destination information. During the data phase, P_AD31

–

P_AD0 contain data.

P_C/BE3

P_C/BE2

P_C/BE1

P_C/BE0

64

79

92

110

I/O

Primary bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During

the address phase of a primary bus PCI cycle, P_C/BE3

–

P_C/BE0 define the bus command. During the data

phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit

data bus carry meaningful data. P_C/BE0 applies to byte 0 (P_AD7

–

P_AD0), P_C/BE1 applies to byte 1

(P_AD15

–

P_AD8), P_C/BE2 applies to byte 2 (P_AD23

–

P_AD16), and P_C/BE3 applies to byte 3

(P_AD31

–

P_AD24).

相關PDF資料 |

PDF描述 |

|---|---|

| PCI2050PDV | BUS CONTROLLER |

| PCI9054AB50BI | Interface IC |

| PCI9036 | Telecommunication IC |

| PCI9050 | PCI Bus Interface/Controller |

| PCI9050-1 | PCI Bus Interface/Controller |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PCI2050IGHK | 功能描述:外圍驅動器與原件 - PCI 32B 33 MHz PCI-to- PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI2050IPDV | 功能描述:外圍驅動器與原件 - PCI 32B 33 MHz PCI-to- PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI2050IPDVG4 | 功能描述:外圍驅動器與原件 - PCI 32B 33 MHz PCI-to- PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI2050IZHK | 功能描述:外圍驅動器與原件 - PCI 32B 33 MHz PCI-to- PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI2050PDV | 功能描述:外圍驅動器與原件 - PCI 32B 33 MHz PCI-to- PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。