- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367816 > PCF2113F2 (NXP Semiconductors N.V.) LCD controller/driver(LCD控制器/驅(qū)動(dòng)器) PDF資料下載

參數(shù)資料

| 型號(hào): | PCF2113F2 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | LCD controller/driver(LCD控制器/驅(qū)動(dòng)器) |

| 中文描述: | LCD控制器/驅(qū)動(dòng)器(液晶顯示控制器/驅(qū)動(dòng)器) |

| 文件頁數(shù): | 8/60頁 |

| 文件大小: | 392K |

| 代理商: | PCF2113F2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

1997 Apr 04

8

Philips Semiconductors

Product specification

LCD controller/driver

PCF2113x

8

FUNCTIONAL DESCRIPTION

(see Fig.1)

8.1

LCD supply voltage generator

The LCD supply voltage may be generated on-chip.

The voltage generator is controlled by two internal 6-bit

registers, V

A

and V

B

. The nominal LCD operating voltage

at room temperature is given by the relationships:

V

OP(nom)

= [(integer value of register)

×

0.08 + 1.9] V

8.2

Programming ranges (

T

ref

= 27

°

C)

Programmed value range: 1 to 63.

Voltage range: 1.90 to 6.84 V.

Values producing more than 6.5 V at operating

temperature are not allowed.

Operation above this

voltage may damage the device. When programming the

operating voltage the V

LCD

temperature coefficient must

be taken into account.

Values below 2.2 V are below the specified operating

range of the chip and are therefore not allowed.

Value 0 for V

A

and V

B

switches the generator off.

Usually register V

A

is programmed with the voltage for

character mode and register V

B

with the voltage for icon

mode. V

B

must be programmed to FF in character mode

and V

A

must be programmed to 00 in icon mode.

When V

LCD

is generated on-chip the V

LCD

pins should be

decoupled to V

SS

with a suitable capacitor. The generated

V

LCD

is independent of V

DD

and is temperature

compensated. When the generator is switched off an

external voltage may be supplied at connected pins

V

LCD1,2

. V

LCD1,2

may be higher or lower than V

DD

if

external V

LCD

is used.

If internally generated it must not

be lower than V

DD

and

V

DD

.

8.3

LCD bias voltage generator

The intermediate bias voltages for the LCD display are

also generated on-chip. This removes the need for an

external resistive bias chain and significantly reduces the

system current consumption. The optimum value of V

LCD

depends on the multiplex rate, the LCD threshold voltage

(V

th

) and the number of bias levels and is given by the

relationships given in Tables 1 and 2. Using a 5-level bias

scheme for 1 : 18 maximum rate allows V

LCD

< 5 V for

most LCD liquids.

4V

≤

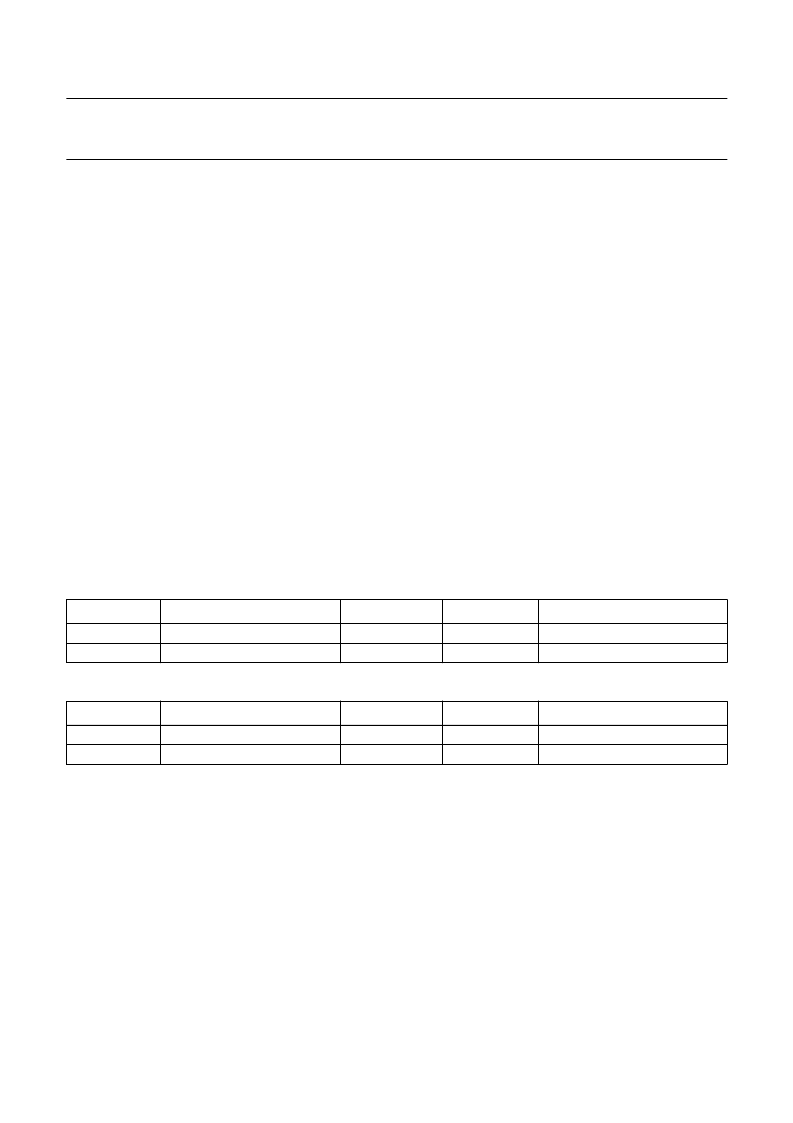

Table 1

Optimum/maximum values for V

OP

(off pixels start darkening; V

off

= V

th

)

Table 2

Minimum values for V

OP

(on pixels clearly visible; V

on

> V

th

)

MUX RATE

NUMBER OF LEVELS

V

on

/V

th

1.272

2.236

V

OP

/V

th

3.7

2.283

V

OP

(typical; for V

th

= 1.4 V)

5.2 V

3.9 V

1 : 18

1 : 2

5

3

MUX RATE

NUMBER OF LEVELS

V

on

/V

th

1.12

1.2

V

OP

/V

th

3.2

1.5

V

OP

(typical; for V

th

= 1.4 V)

4.6 V

2.1 V

1 : 18

1 : 2

5

3

8.4

Oscillator

The on-chip oscillator provides the clock signal for the

display system. No external components are required and

the OSC pin must be connected to V

DD

.

8.5

External clock

If an external clock is to be used this is input at the OSC

pin. The resulting display frame frequency is given by

f

f

frame

3072

=

Only in the power-down state is the clock allowed to be

stopped (OSC connected to V

ss

), otherwise the LCD is

frozen in a DC state.

8.6

Power-on reset

The on-chip power-on reset block initializes the chip after

power-on or power failure. This is a synchronous reset and

requires 3 OSC cycles to be executed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF211310 | LCD controller/driver(LCD控制器/驅(qū)動(dòng)器) |

| PCF21132 | LCD controller/driver(LCD控制器/驅(qū)動(dòng)器) |

| PCF211410 | LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) |

| PCF2116AHZ | JT 66C 66#22D PIN RECP |

| PCF2116CHZ | LCD controller/drivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF2113FAMILY | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| PCF2113WU | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LCD controllers/drivers |

| PCF2113WU/2/F4 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LCD controllers/drivers |

| PCF2113WU/2/F4,026 | 功能描述:IC LCD CTLR/DRIVER UNCASED RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| PCF2113WU2 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LCD controllers/drivers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。