- 您現在的位置:買賣IC網 > PDF目錄369946 > PALCE22V10-25KMB (CYPRESS SEMICONDUCTOR CORP) Flash-erasable Reprogrammable CMOS PAL Device PDF資料下載

參數資料

| 型號: | PALCE22V10-25KMB |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | Flash-erasable Reprogrammable CMOS PAL Device |

| 中文描述: | FLASH PLD, 25 ns, CDFP24 |

| 封裝: | CERPACK-24 |

| 文件頁數: | 6/13頁 |

| 文件大?。?/td> | 367K |

| 代理商: | PALCE22V10-25KMB |

PALCE22V10

USE ULTRA37000

TM

FOR

ALL NEW DESIGNS

Document #: 38-03027 Rev. *B

Page 6 of 13

t

S1

t

S2

Input or Feedback Set-Up Time

Synchronous Preset Set-Up

Time

Input Hold Time

External Clock Period (t

CO

+ t

S

)

Clock Width HIGH

[6]

Clock Width LOW

[6]

External Maximum

Frequency (1/(t

CO

+ t

S

))

[11]

Data Path Maximum Frequency

(1/(t

WH

+ t

WL

))

[6, 12]

Internal Feedback Maximum

Frequency (1/(t

CF

+ t

S

))

[6,13]

Register Clock to

Feedback Input

[6,14]

Asynchronous Reset Width

Asynchronous Reset

Recovery Time

Asynchronous Reset to

Registered Output Delay

Synchronous Preset

Recovery Time

Power-up Reset Time

[6,15]

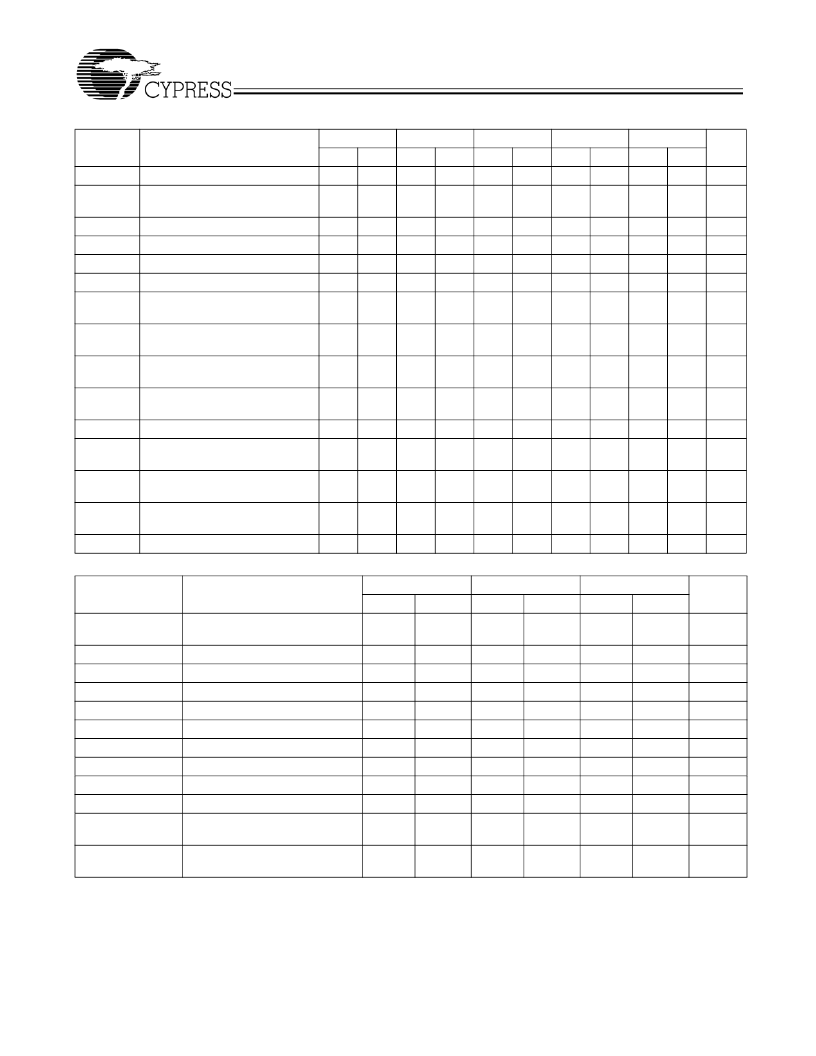

Military and Industrial Switching Characteristics PALCE22V10

[2, 7]

3

4

5

6

6

7

10

10

15

15

ns

ns

t

H

t

P

t

WH

t

WL

f

MAX1

0

7

0

10

3

3

100

0

12

3

3

76.9

0

20

6

6

55.5

0

30

13

13

33.3

ns

ns

ns

ns

MHz

2.5

2.5

143

f

MAX2

200

166

142

83.3

35.7

MHz

f

MAX3

181

133

111

68.9

38.5

MHz

t

CF

2.5

2.5

3

4.5

13

ns

t

AW

t

AR

8

4

8

5

10

6

15

10

25

25

ns

ns

t

AP

7.5

12

13

20

25

ns

t

SPR

4

6

8

10

15

ns

t

PR

1

1

1

1

1

μ

s

Parameter

Description

22V10-10

Min.

3

22V10-15

Min.

3

22V10-25

Min.

3

Unit

ns

Max.

10

Max.

15

Max.

25

t

PD

Input to Output

Propagation Delay

[8]

Input to Output Enable Delay

[9]

Input to Output Disable Delay

[10]

Clock to Output Delay

[8]

Input or Feedback Set-up Time

Synchronous Preset Set-up Time

Input Hold Time

External Clock Period (t

CO

+ t

S

)

Clock Width HIGH

[6]

Clock Width LOW

[6]

External Maximum Frequency

(1/(t

CO

+ t

S

))

[11]

Data Path Maximum Frequency

(1/(t

WH

+ t

WL

))

[6, 12 ]

t

EA

t

ER

t

CO

t

S1

t

S2

t

H

t

P

t

WH

t

WL

f

MAX1

10

10

7

15

15

8

25

25

15

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

2

6

7

0

12

3

3

76.9

2

2

10

10

0

20

6

6

50.0

18

18

0

33

14

14

30.3

f

MAX2

142

83.3

35.7

MHz

Notes:

11. This specification indicates the guaranteed maximum frequency at which a state machine configuration with external feedback can operate.

12.This specification indicates the guaranteed maximum frequency at which the device can operate in data path mode.

13.This specification indicates the guaranteed maximum frequency at which a state machine configuration with internal only feedback can operate.

14.This parameter is calculated from the clock period at f

internal (1/f

) as measured (see Note above) minus t

.

15.The registers in the PALCE22V10 have been designed with the capability to reset during system power-up. Following power-up, all registers will be reset to a

logic LOW state. The output state will depend on the polarity of the output buffer. This feature is useful in establishing state machine initialization. To insure proper

operation, the rise in V

CC

must be monotonic and the timing constraints depicted in Power-Up Reset Waveform must be satisfied.

Commercial Switching Characteristics PALCE22V10

(continued)

[2, 7]

Parameter

Description

22V10-5

Min.

22V10-7

Min.

22V10-10

Min.

22V10-15

Min.

22V10-25

Min.

Unit

Max.

Max.

Max.

Max.

Max.

相關PDF資料 |

PDF描述 |

|---|---|

| PALCE22V10-25PI | Flash-erasable Reprogrammable CMOS PAL Device |

| PALC22V10B | Reprogrammable CMOS PAL Device |

| PALC22V10D | FLASG ERASABLE REPROGRAMMABLE CMOS PAL DEVICE |

| PALC22V10 | ECONOLINE: RSS & RSD - 1kVDC and 3KVDC Isolation- Internal SMD Construction- UL94V-0 Package Material- Toroidal Magnetics- Efficiency to 85%- SMD5, SMD8, SMD10 and SMD12 case styles |

| PALCE22V10 | Flash Erasable,Reprogrammable CMOS PAL Device(可擦除閃速,CMOS可重編程PAL器件) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PALCE22V10-25LMB | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Flash Erasable, Reprogrammable CMOS PAL㈢ Device |

| PALCE22V10-25PC | 制造商:Cypress Semiconductor 功能描述: |

| PALCE22V10-25PI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Flash Erasable, Reprogrammable CMOS PAL㈢ Device |

| PALCE22V10-5 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Flash-erasable Reprogrammable CMOS PAL Device |

| PALCE22V10-5AC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable PLD |

發(fā)布緊急采購,3分鐘左右您將得到回復。