- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369944 > P89LPC915 (NXP Semiconductors N.V.) 8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter PDF資料下載

參數(shù)資料

| 型號: | P89LPC915 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter |

| 中文描述: | 8 - 8加速雙位單片機80C51的時鐘核心2 Kb的3伏閃存位A / D轉(zhuǎn)換器 |

| 文件頁數(shù): | 30/72頁 |

| 文件大?。?/td> | 344K |

| 代理商: | P89LPC915 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

Philips Semiconductors

P89LPC915/916/917

8-bit microcontrollers with accelerated two-clock 80C51 core

Product data

Rev. 04 — 17 December 2004

30 of 72

9397 750 14397

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

9.4 Watchdog oscillator option

The Watchdog has a separate oscillator which has a frequency of 400 kHz. This

oscillator can be used to save power when a high clock frequency is not needed.

9.5 External clock input option

In this configuration, the processor clock is derived from an external source driving

the CLKIN pin. The rate may be from 0 Hz up to 18 MHz.

When using an oscillator

frequency above 12 MHz, the reset input function of P1.5 must be enabled. An

external circuit is required to hold the device in reset at power-up until V

DD

has

reached its specified level. When system power is removed V

DD

will fall below

the minimum specified operating voltage. When using an oscillator frequency

above 12 MHz, in some applications, an external brownout detect circuit may

be required to hold the device in reset when V

DD

falls below the minimum

specified operating voltage.

9.6 CPU Clock (CCLK) wake-up delay

The P89LPC915/916/917 has an internal wake-up timer that delays the clock until it

stabilizes. The delay is 224 OSCCLK cycles plus 60 to 100

μ

s.

9.7 CPU Clock (CCLK) modification: DIVM register

The OSCCLK frequency can be divided down up to 510 times by configuring a

dividing register, DIVM, to generate CCLK. This feature makes it possible to

temporarily run the CPU at a lower rate, reducing power consumption. By dividing the

clock, the CPU can retain the ability to respond to events that would not exit Idle

mode by executing its normal program at a lower rate. This can also allow bypassing

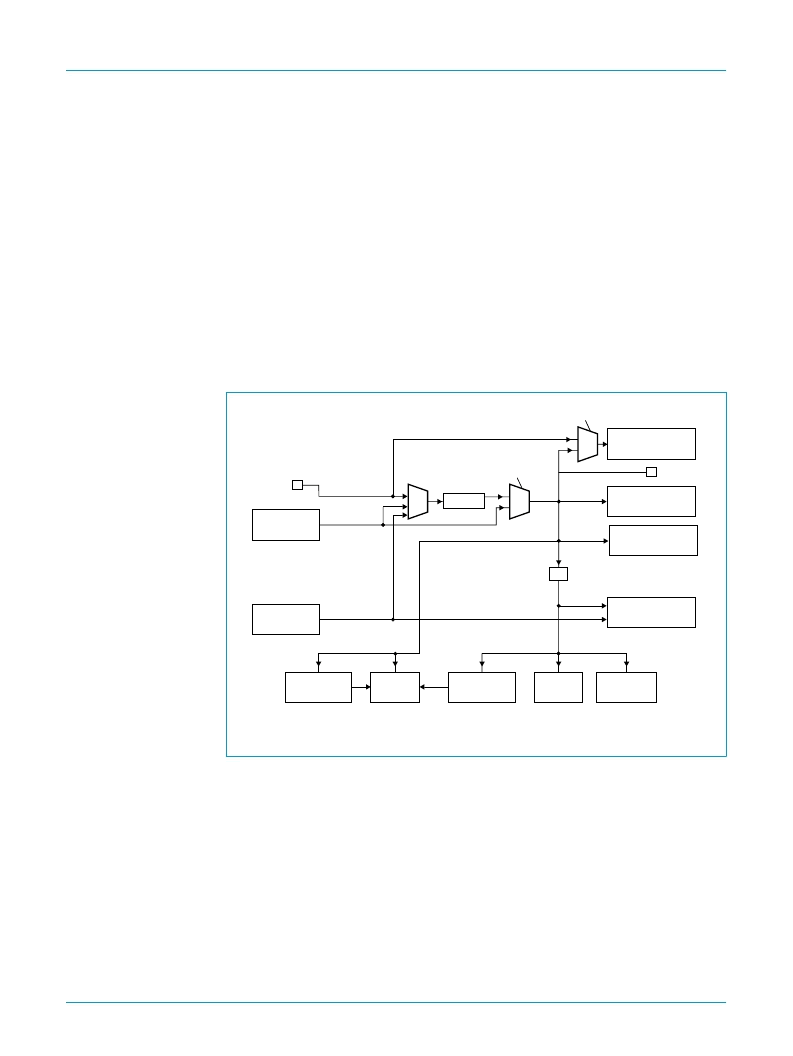

Fig 10. Block diagram of oscillator control.

÷

2

002aaa831

RTC

CPU

WDT

DIVM

CCLK

OSCCLK

XCLK

RCCLK

I

2

C

PCLK

peripheral clock

TIMERS 1 & 0

CLKIN

RC

OSCILLATOR

WATCHDOG

OSCILLATOR

(7.3728 MHz)

(400 kHz)

PCLK

RCCLK

SPI

(P89LPC916)

RTCS1:0

ADC1/DAC1

UART

BAUD RATE

GENERATOR

CLKOUT

相關PDF資料 |

PDF描述 |

|---|---|

| P89LPC915HDH | 8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter |

| P89LPC916 | 8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter |

| P89LPC917 | 8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter |

| P89LPC932A1 | 8-Bit Microcontroller with accelerated two-clock 80C51 core 8kB 3V byte-erasable flash with 512-byte data EEPROM |

| P89LPC932 | 80C51 8-bit microcontroller with two-clock core 8 KB 3 V low-power Flash with 512-byte data EEPROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| P89LPC9151 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core, 2 kB 3 V byte-erasable flash with 8-bit ADC |

| P89LPC9151FDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core, 2 kB 3 V byte-erasable flash with 8-bit ADC |

| P89LPC9151FDH,129 | 功能描述:8位微控制器 -MCU IC 80C51 MCU FLASH 2KB RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| P89LPC915FDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontrollers with accelerated two-clock 80C51 core 2 kB 3 V Flash with 8-bit A/D converter |

| P89LPC915FDH,129 | 功能描述:8位微控制器 -MCU 80C51 2K FL 256B RAM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。