- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367723 > P87C591SFB (NXP SEMICONDUCTORS) Single-chip 8-bit microcontroller with CAN controller PDF資料下載

參數(shù)資料

| 型號(hào): | P87C591SFB |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Single-chip 8-bit microcontroller with CAN controller |

| 中文描述: | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | 10 X 10 X 1.75 MM, PLASTIC, SOT-307-2, QFP-44 |

| 文件頁數(shù): | 99/161頁 |

| 文件大?。?/td> | 588K |

| 代理商: | P87C591SFB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁當(dāng)前第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

1999 Aug 19

99

Philips Semiconductors

Objective Specification

Single-chip 8-bit microcontroller with CAN controller

P8xC591

15.2.15.3 I

2

C bus obstructed by a low level on SCL and

SDA

An I

2

C bus hang-up occurs if SDA or SCL is pulled LOW

by an uncontrolled source. If the SCL line is obstructed

(pulled LOW) by a device on the bus, no further serial

transfer is possible, and the SIO1 hardware cannot resolve

this type of problem. When this occurs, the problem must

be resolved by the device that is pulling the SCL bus line

LOW.

If the SDA line is obstructed by another device on the bus

(e.g., a slave device out of bit synchronization), the

problem can be solved by transmitting additional clock

pulses on the SCL line (see Figure 43). The SIO1

hardware transmits additional clock pulses when the STA

flag is set, but no START condition can be generated

because the SDA line is pulled LOW while the I

2

C bus is

considered free.

The SIO1 hardware attempts to generate a START

condition after every two additional clock pulses on the

SCL line. When the SDA line is eventually released, a

normal START condition is transmitted, state 08H is

entered, and the serial transfer continues.

If a forced bus access occurs or a repeated START

condition is transmitted while SDA is obstructed (pulled

LOW), the SIO1 hardware performs the same action as

described above. In each case, state 08H is entered after

a successful START condition is transmitted and normal

serial transfer continues. Note that the CPU is not involved

in solving these bus hang-up problems.

15.2.15.4 Bus error

A bus error occurs when a START or STOP condition is

present at an illegal position in the format frame. Examples

of illegal positions are during the serial transfer of an

address byte, a data or an acknowledge bit.

The SIO1 hardware only reacts to a bus error when it is

involved in a serial transfer either as a master or an

addressed slave. When a bus error is detected, SIO1

immediately switches to the not addressed slave mode,

releases the SDA and SCL lines, sets the interrupt flag,

and loads the status register with 00H. This status code

may be used to vector to a service routine which either

attempts the aborted serial transfer again or simply

recovers from the error condition as shown in Table 65.

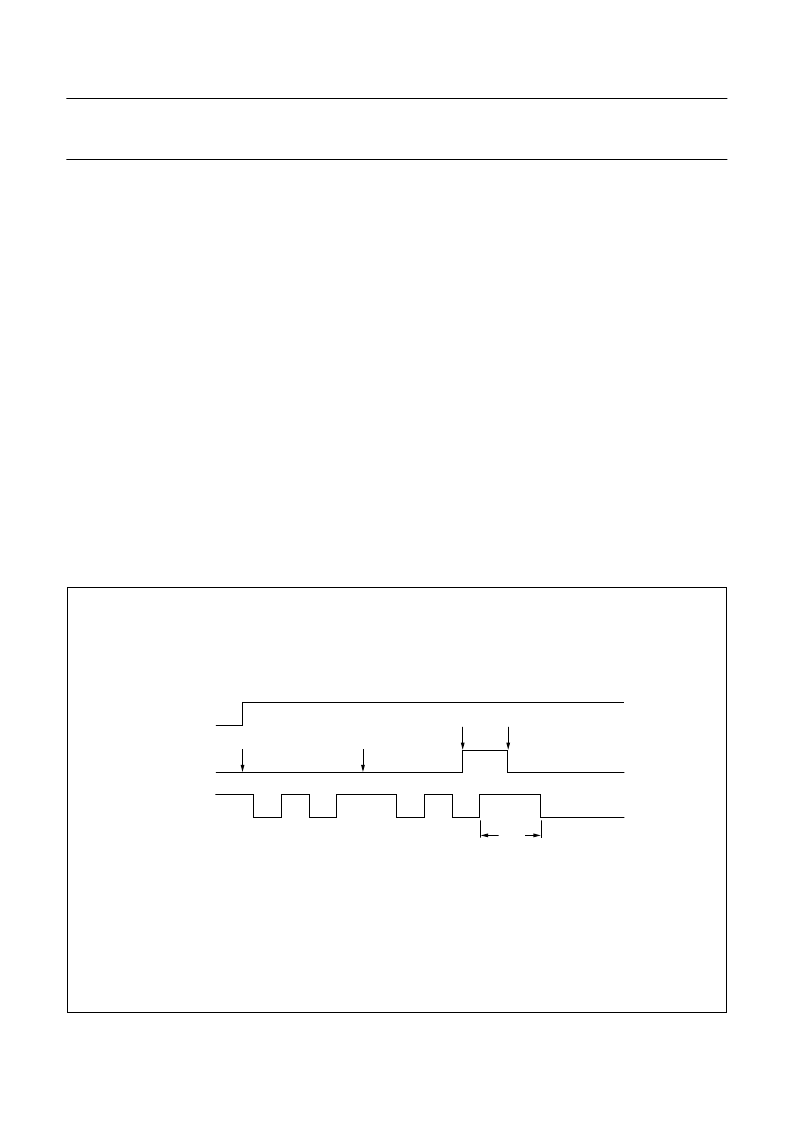

Fig.43 Recovering from a bus obstruction caused by a low level on SDA.

handbook, full pagewidth

MHI044

STA FLAG

SDA LINE

SCL LINE

(1)

(1)

(2)

(3)

start

condition

(1) Unsuccessful attempt to send a Start condition.

(2) SDA line released.

(3) Successful attempt to send a Start condition; state D8H is centered.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P80C591 | Single-chip 8-bit microcontroller with CAN controller |

| P83C591 | Single-chip 8-bit microcontroller with CAN controller |

| P87C591 | Single-chip 8-bit microcontroller with CAN controller |

| P83C591VFA | Single-chip 8-bit microcontroller with CAN controller |

| P80CE560 | 8-BIT SINGLE CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P87C591VFA/00,512 | 功能描述:8位微控制器 -MCU 80C51 16K OTP/CAN RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| P87C654X2BBD,157 | 功能描述:8位微控制器 -MCU 16K/256 OTP 12/6 CLK I2C LQFP RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| P87C654X2FA | 制造商:NXP Semiconductors 功能描述:P87C654X2FA 8bit microcontroller,33MHz |

| P87C654X2FA,529 | 功能描述:8位微控制器 -MCU 16K/256 OTP 12/6 CLK RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| P87C654X2FA-S | 功能描述:8位微控制器 -MCU 16K/256 OTP 12/6 CLK I2C PLCC RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。