- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369944 > P83C524EFP (NXP SEMICONDUCTORS) CONN HEADER 12POS SGL PCB 30GOLD PDF資料下載

參數(shù)資料

| 型號: | P83C524EFP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CONN HEADER 12POS SGL PCB 30GOLD |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | 0.600 INCH, PLASTIC, DIP-40 |

| 文件頁數(shù): | 57/76頁 |

| 文件大小: | 400K |

| 代理商: | P83C524EFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

1997 Dec 15

57

Philips Semiconductors

Product specification

8-bit microcontrollers

P83C524; P80C528; P83C528

21.2

See notes 1, 2 and 3.; Cl = 100 pF for Port 0, ALE and PSEN; C

L

= 80 pF for all other outputs unless otherwise

specified.

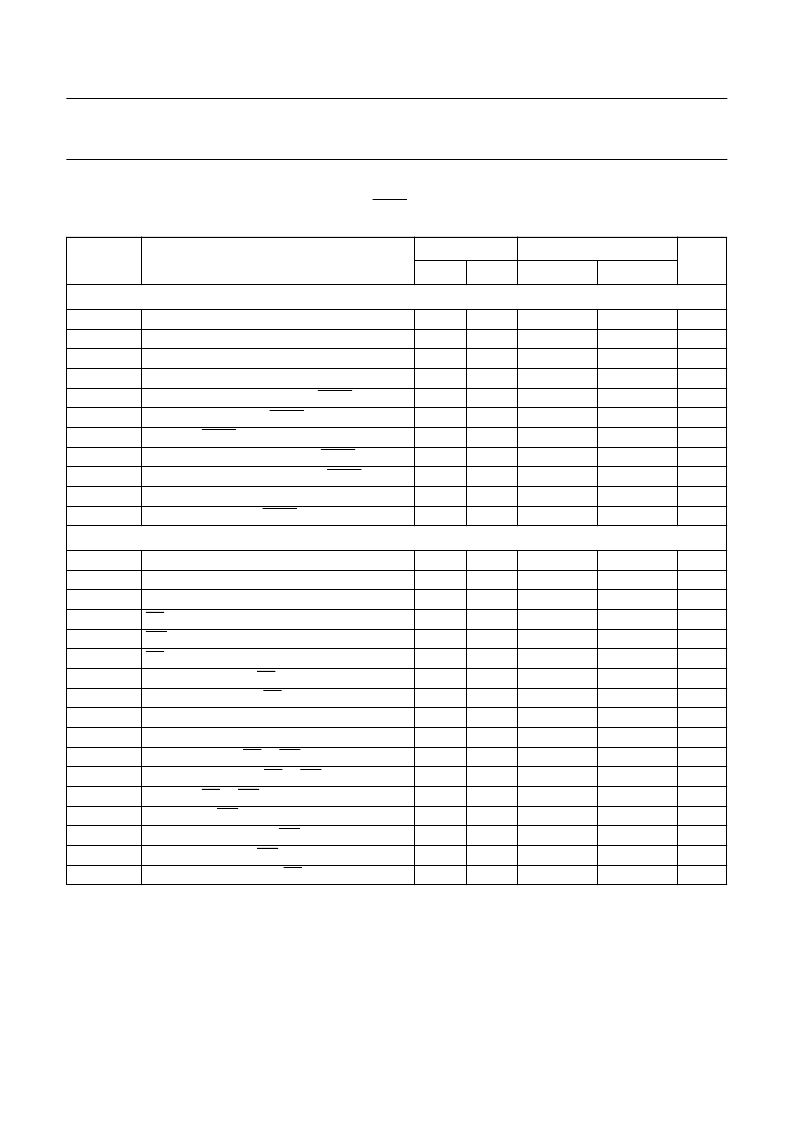

AC Characteristics 24 MHz version

Notes to the AC Characteristics 16 and 24 MHz versions

1.

For the AC Characteristics the following conditions are valid:

a)

P83C52x EBx

: V

DD

= 5 V

±

10%; V

SS

= 0 V; T

amb

= 0 to +70

°

C; t

CK

min. = 63 ns

b)

P83C52x EFx:

V

DD

= 5 V

±

10%; V

SS

= 0 V; T

amb

=

40 to +85

°

C; t

CK

min. = 63 ns.

2.

t

CK

min. = 1/f max. (maximum operating frequency); t

CK

= clock period (see section for timing symbol definitions).

3.

The maximum operating frequency is limited to 16/24 MHz and the minimum to 3.5 MHz (all versions Ixx/Exx).

SYMBOL

PARAMETER

24 MHZ

VARIABLE CLOCK

UNIT

MIN.

MAX.

MIN.

MAX.

External program memory

t

LHLL

t

AVLL

t

LLAX

t

LLIV

t

LLPL

t

PLPH

t

PLIV

t

PXIX

t

PXIZ

t

AVIV

t

PLAZ

ALE pulse duration

address set-up time to ALE

address hold time after ALE

time from ALE to valid instruction input

time from ALE to control pulse PSEN

control pulse duration PSEN

time from PSEN to valid instruction input

input instruction hold time after PSEN

input instruction float delay after PSEN

address to valid instruction input

address float time to PSEN

43

17

17

17

80

0

102

65

17

128

10

2 t

CK

40

t

CK

25

t

CK

25

t

CK

25

3 t

CK

45

0

4 t

CK

65

3 t

CK

60

t

CK

25

5 t

CK

80

10

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

External data memory

t

LHLL

t

AVLL

t

LLAX

t

RLRH

t

WLWH

t

RLDV

t

RHDX

t

RHDZ

t

LLDZ

t

AVDV

t

LLWL

t

AVWL

t

WHLH

t

QVWX

t

QVWH

t

WHQX

t

RLAZ

ALE pulse duration

address set-up time to ALE

address hold time after ALE

RD pulse duration

WR pulse duration

RD to valid data input

data hold time after RD

data float delay after RD

time from ALE to valid data input

address to valid data input

time from ALE to RD or WR

time from address to RD or WR

time from RD or WR HIGH to ALE HIGH

data valid to WR transition

data set-up time before WR

data hold time after WR

address float delay after RD

43

17

17

150

150

0

75

92

17

12

162

17

118

55

183

210

175

67

0

2 t

CK

40

t

CK

25

t

CK

25

6 t

CK

100

6 t

CK

100

0

3 t

CK

50

4 t

CK

75

t

CK

25

t

CK

30

7 t

CK

130

t

CK

25

5 t

CK

90

2 t

CK

28

8 t

CK

150

9 t

CK

165

3 t

CK

+50

t

CK

+ 25

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C524IBA | 8-bit microcontrollers |

| P83C524IBB | 8-bit microcontrollers |

| P83C524IFB | 8-bit microcontrollers |

| P83C524IFP | 8-bit microcontrollers |

| P83C524IBP | 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C524FFA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P83C524FFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P83C524FHA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P83C524FHP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P83C524GFA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。