- 您現(xiàn)在的位置:買賣IC網 > PDF目錄363670 > NT5SV32M8AT-7K (Electronic Theatre Controls, Inc.) 256Mb Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | NT5SV32M8AT-7K |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 256Mb Synchronous DRAM |

| 中文描述: | 256Mb的同步DRAM |

| 文件頁數(shù): | 9/65頁 |

| 文件大小: | 814K |

| 代理商: | NT5SV32M8AT-7K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

NT5SV64M4AT(L)

NT5SV32M8AT(L)

NT5SV16M16AT(L)

256Mb Synchronous DRAM

REV 1.0

May, 2001

9

NANYA TECHNOLOGY CORP

. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

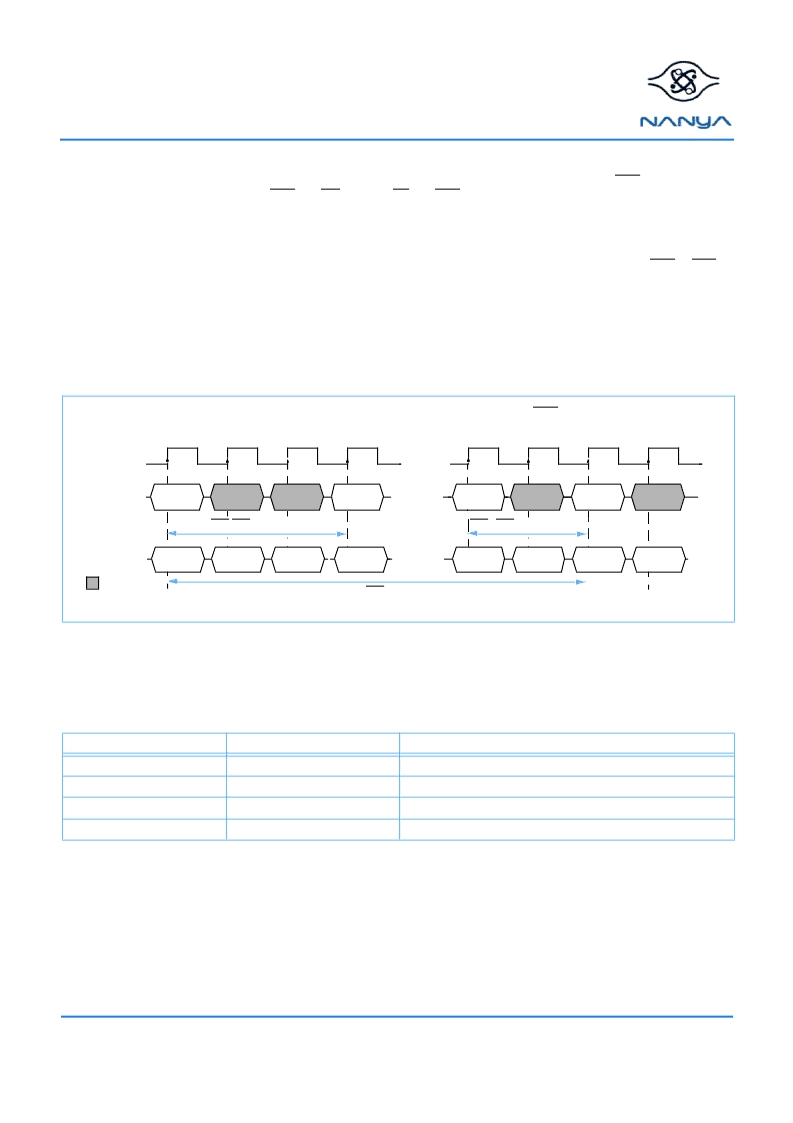

Bank Activate Command

In relation to the operation of a fast page mode DRAM, the Bank Activate command correlates to a falling RAS signal.

The Bank

Activate command is issued by holding CAS and WE high with CS and RAS low at the rising edge of the clock. The Bank Select

address BA0 - BA1 is used to select the desired bank. The row address A0 - A12 is used to determine which row to activate in

the selected bank.

The Bank Activate command must be applied before any Read or Write operation can be executed. The delay from when the

Bank Activate command is applied to when the first read or write operation can begin must meet or exceed the RAS to CAS

delay time (t

RCD

). Once a bank has been activated it must be precharged before another Bank Activate command can be

applied to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is deter-

mined by the RAS cycle time of the device (t

RC

). The minimum time interval between interleaved Bank Activate commands

(Bank A to Bank B and vice versa) is the Bank to Bank delay time (t

RRD

). The maximum time that each bank can be held active

is specified as t

RAS(max)

.

Bank Select

The Bank Select inputs, BA0 and BA1, determine the bank to be used during a Bank Activate, Precharge, Read, or Write oper-

ation.

Bank Activate Command Cycle

Bank Selection Bits

BA0

BA1

Bank

0

0

Bank 0

1

0

Bank 1

0

1

Bank 2

1

1

Bank 3

ADDRESS

CK

T0

T2

T1

T3

Tn

Tn+1

Tn+2

Tn+3

COMMAND

NOP

NOP

NOP

NOP

Bank A

Row Addr.

Bank A

Activate

PWrite A

Bank A

Col. Addr.

. . . . . . . . . .

. . . . . . . . . .

. . . . . . . . . .

Bank B

Activate

Bank A

Row Addr.

Bank A

Activate

RAS-CAS delay (

t

RCD

)

: “H” or “L”

RAS Cycle time (

t

RC

)

RAS - RAS delay time (

t

RRD

)

Bank B

Row Addr.

(CAS Latency = 3, t

RCD

= 3)

相關PDF資料 |

PDF描述 |

|---|---|

| NT5SV32M8AT-8B | 256Mb Synchronous DRAM |

| NT5SV64M4AT | 256Mb Synchronous DRAM |

| NT5SV64M4AT-7K | 256Mb Synchronous DRAM |

| NT5SV64M4AT-8B | 256Mb Synchronous DRAM |

| NT5SV64M4AT-75B | 256Mb Synchronous DRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| NT5SV32M8AT-8B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:256Mb Synchronous DRAM |

| NT5SV4M16DT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64Mb Synchronous DRAM |

| NT5SV4M16DT-6K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64Mb Synchronous DRAM |

| NT5SV4M16DT-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64Mb Synchronous DRAM |

| NT5SV4M16DT7K | 制造商:Nanya Technology Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。