- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369933 > MTB9N25E (MOTOROLA INC) TMOS POWER FET 9.0 AMPERES 250 VOLTS PDF資料下載

參數(shù)資料

| 型號: | MTB9N25E |

| 廠商: | MOTOROLA INC |

| 元件分類: | JFETs |

| 英文描述: | TMOS POWER FET 9.0 AMPERES 250 VOLTS |

| 中文描述: | 9 A, 250 V, 0.45 ohm, N-CHANNEL, Si, POWER, MOSFET |

| 文件頁數(shù): | 5/10頁 |

| 文件大小: | 258K |

| 代理商: | MTB9N25E |

5

Motorola TMOS Power MOSFET Transistor Device Data

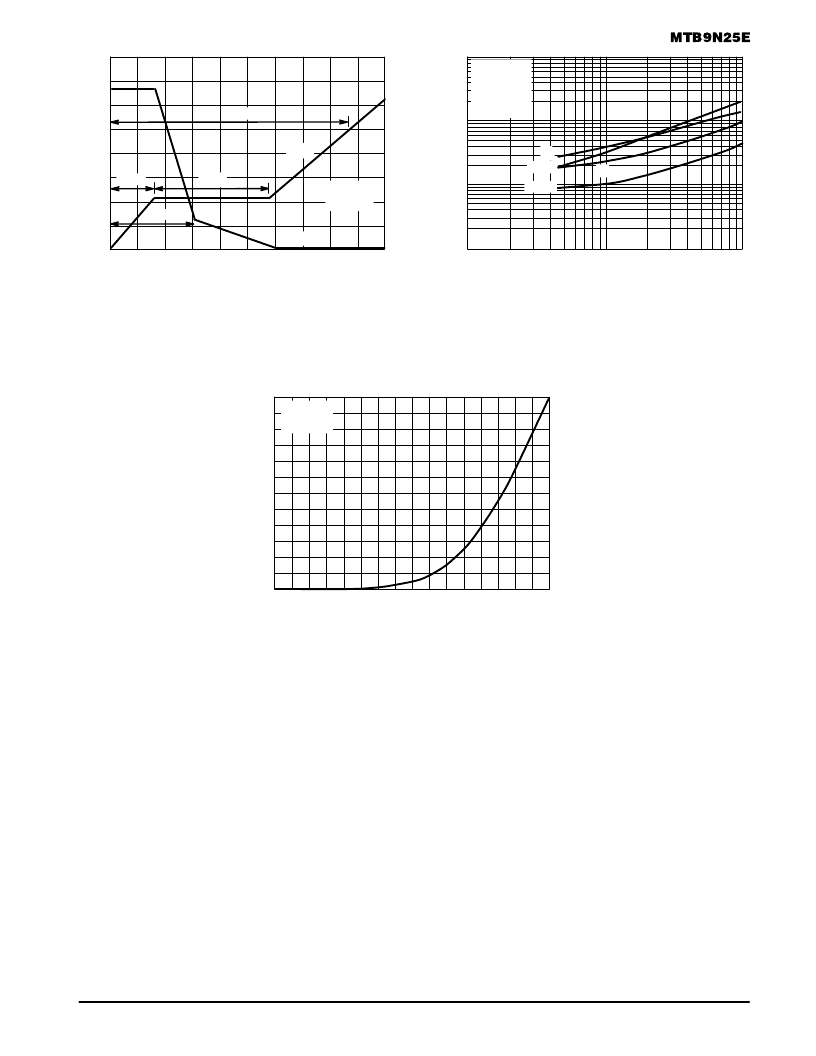

DRAIN–TO–SOURCE DIODE CHARACTERISTICS

Figure 10. Diode Forward Voltage versus Current

Figure 9. Resistive Switching Time

Variation versus Gate Resistance

Figure 8. Gate–To–Source and Drain–To–Source

Voltage versus Total Charge

RG, GATE RESISTANCE (OHMS)

1

10

100

100

1

t

tf

td(off)

td(on)

240

V

180

120

60

0

16

0

QT, TOTAL CHARGE (nC)

V

12

8

4

6

12

18

30

VDS

VGS

24

0

Q1

Q2

QT

Q3

10

tr

VDD = 250 V

ID = 9 A

VGS = 10 V

TJ = 25

°

C

ID = 9 A

TJ = 25

°

C

1000

0.5

0.6

0.7

0.8

0.9

0

3.0

6.0

9.0

VSD, SOURCE–TO–DRAIN VOLTAGE (VOLTS)

I

VGS = 0 V

TJ = 25

°

C

7.5

4.5

0.55

0.65

0.75

0.85

1.5

SAFE OPERATING AREA

The Forward Biased Safe Operating Area curves define

the maximum simultaneous drain–to–source voltage and

drain current that a transistor can handle safely when it is for-

ward biased. Curves are based upon maximum peak junc-

tion temperature and a case temperature (TC) of 25

°

C. Peak

repetitive pulsed power limits are determined by using the

thermal response data in conjunction with the procedures

discussed in AN569, “Transient Thermal Resistance–Gener-

al Data and Its Use.”

Switching between the off–state and the on–state may tra-

verse any load line provided neither rated peak current (IDM)

nor rated voltage (VDSS) is exceeded and the transition time

(tr,tf) do not exceed 10

μ

s. In addition the total power aver-

aged over a complete switching cycle must not exceed

(TJ(MAX) – TC)/(R

θ

JC).

A Power MOSFET designated E–FET can be safely used

in switching circuits with unclamped inductive loads. For reli-

able operation, the stored energy from circuit inductance dis-

sipated in the transistor while in avalanche must be less than

the rated limit and adjusted for operating conditions differing

from those specified. Although industry practice is to rate in

terms of energy, avalanche energy capability is not a con-

stant. The energy rating decreases non–linearly with an in-

crease of peak current in avalanche and peak junction

temperature.

Although many E–FETs can withstand the stress of drain–

to–source avalanche at currents up to rated pulsed current

(IDM), the energy rating is specified at rated continuous cur-

rent (ID), in accordance with industry custom. The energy rat-

ing must be derated for temperature as shown in the

accompanying graph (Figure 12). Maximum energy at cur-

rents below rated continuous ID can safely be assumed to

equal the values indicated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTD2955V | TMOS POWER FET 12 AMPERES 60 VOLTS RDS(on) = 0.230 OHM |

| MTD2955V | P-Channel Enhancement Mode Field Effect Transistor |

| MTD2N50 | POWER FIELD EFFECT TRANSISTOR N-CHANNEL ENHANCEMENT-MODE SILICON GATE DPAK FOR SURFACE MOUNT OR INSERTION MOUNT |

| MTD6N20E | TMOS POWER FET 6.0 AMPERES 200 VOLTS RDS(on) = 0.7 OHM |

| MTD6P10E | TMOS POWER FET 6.0 AMPERES 100 VOLTS RDS(on) = 0.66 OHM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTB9N25ET4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MTBA5N10J3 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:N -Channel Logic Level Enhancement Mode Power MOSFET |

| MTBA5N10Q8 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:N -Channel Logic Level Enhancement Mode Power MOSFET |

| MTBB0P10J3 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:P-Channel Logic Level Enhancement Mode Power MOSFET |

| MTBB0P10L3 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:P-Channel Logic Level Enhancement Mode Power MOSFET |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。