- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25632 > MPC951FA (INTEGRATED DEVICE TECHNOLOGY INC) 951 SERIES, PLL BASED CLOCK DRIVER, 9 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF資料下載

參數(shù)資料

| 型號: | MPC951FA |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 951 SERIES, PLL BASED CLOCK DRIVER, 9 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封裝: | 7 X 7 MM, LQFP-32 |

| 文件頁數(shù): | 5/10頁 |

| 文件大?。?/td> | 336K |

| 代理商: | MPC951FA |

MPC951

MOTOROLA

TIMING SOLUTIONS

4

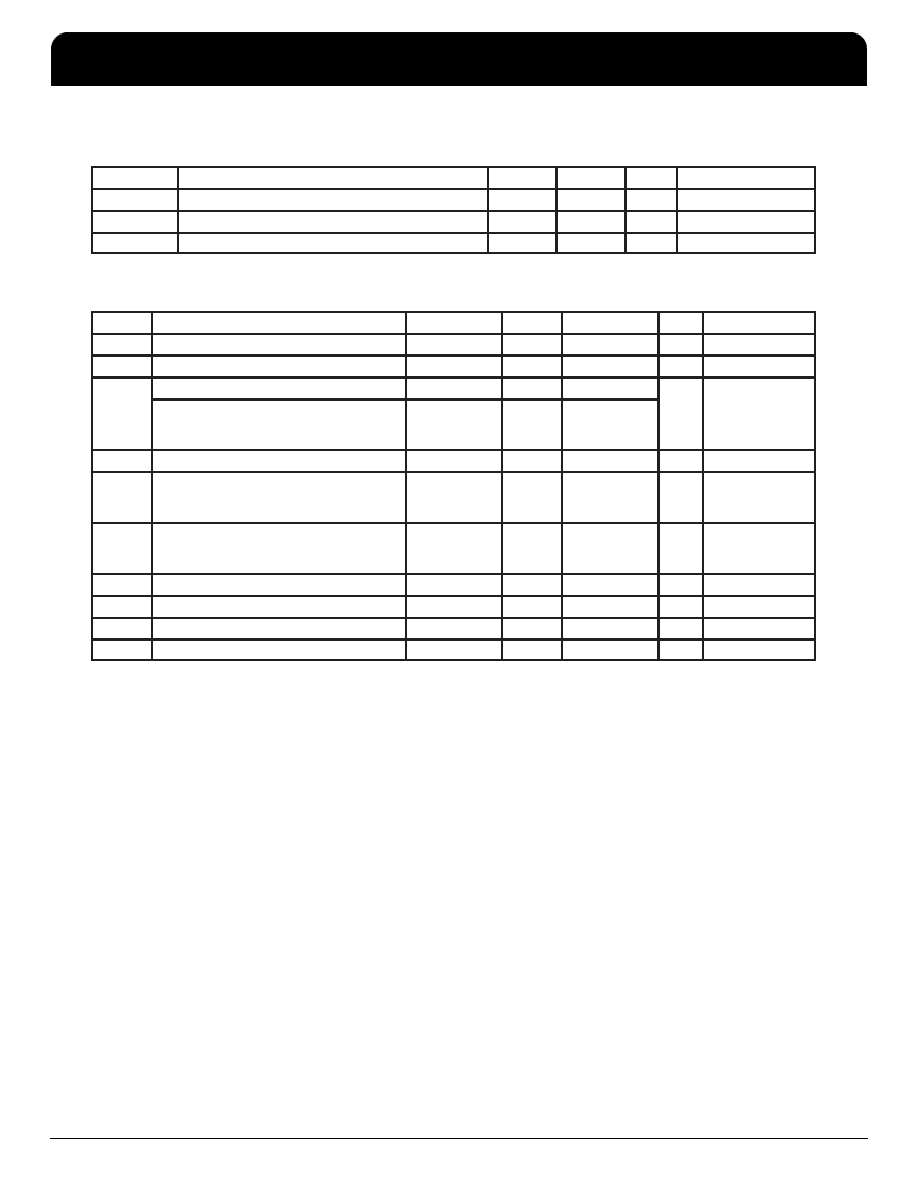

PLL INPUT REFERENCE CHARACTERISTICS (TA = 0 to 70°C)

Symbol

Characteristic

Min

Max

Unit

Condition

tr, tf

TCLK Input Rise/Falls

3.0

ns

fref

Reference Input Frequency

100

MHz

Note 1.

frefDC

Reference Input Duty Cycle

25

75

%

1. Maximum and minimum input reference is limited by the VCO lock range and the feedback divider for the TCLK or PECL_CLK inputs.

AC CHARACTERISTICS (TA = 0°C to 70°C, VCC = 3.3V ±5%)

Symbol

Characteristic

Min

Typ

Max

Unit

Condition

tr, tf

Output Rise/Fall Time

0.10

1.0

ns

0.8 to 2.0V, Note 4.

tpw

Output Duty Cycle

tCYCLE/2–1000

tCYCLE/2+1000

ps

Note 4.

tsk(O)

Output–to–Output Skews

Same Frequencies

200

375

ps

Note 4.

Different Frequencies

Qafmax < 150MHz

Qafmax > 150MHz

325

500

750

fVCO

PLL VCO Lock Range

200

480

MHz

Note 3.

fmax

Maximum Output

Qa (

÷2)

Frequency

Qa/Qb (

÷4)

Qb (

÷8)

180

120

60

MHz

Note 4.

tpd

Input to Ext_FB Delay

TCLK

(Note 1.)

PECL_CLK

50

–950

250

–770

400

–600

ps

fref = 50MHz

Feedback=VCO/8

Note 4.

tPLZ,HZ

Output Disable Time

7

ns

Note 4.

tPZL

Output Enable Time

6

ns

Note 4.

tjitter

Cycle–to–Cycle Jitter (Peak–to–Peak)

±100

ps

Note 2.

tlock

Maximum PLL Lock Time

10

ms

1. The tpd window is specified for a 50Mhz input reference clock. The window will enlarge/reduce proportionally from the minimum limits with an

increase/decrease of the input reference clock period. The tpd does not include jitter.

2. See Applications Info section for more jitter information.

3. The PLL will be unstable with a divide by 2 feedback ratio.

4. Termination of 50

W to VCC/2.

APPLICATIONS INFORMATION

Programming the MPC951

The MPC951 clock driver outputs can be configured into

several frequency relationships. The output dividers for the

four output groups allows the user to configure the outputs

into 1:1, 2:1, 4:1 and 4:2:1 frequency ratios. The use of even

dividers ensures that the output duty cycle is always 50%.

Table 1 illustrates the various output configurations, the table

describes the outputs using the VCO frequency as a

reference. As an example for a 4:2:1 relationship the Qa

outputs would be set at VCO/2, the Qb’s and Qc’s at VCO/4

and the Qd’s at VCO/8. These settings will provide output

frequencies with a 4:2:1 relationship.

The division settings establish the output relationship, but

one must still ensure that the VCO will be stable given the

frequency of the outputs desired. The feedback frequency

should be used to situate the VCO into a frequency range in

which the PLL will be stable. The design of the PLL is such

that for output frequencies between 25 and 180MHz the

MPC951 can generally be configured into a stable region.

The relationship between the input reference and the

output frequency is also very flexible. Table 1 can be used to

determine the multiplication factor, there are too many

potential combinations to tabularize the external feedback

condition. Figure 1 through Figure 2 illustrates several

programming possibilities, although not exhaustive it is

representative of the potential applications.

MPC951

Low Voltage PLL Clock Driver

NETCOM

IDT Low Voltage PLL Clock Driver

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MPC951

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC961CFA | 961 SERIES, PLL BASED CLOCK DRIVER, 17 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| MPC962304D-1R2 | 962304 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| MPC96877EP | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| MPC97R73FA | PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC9892FA | PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC951FAR2 | 制造商:Motorola Inc 功能描述: |

| MPC952 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC953 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC958 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC9600 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:LOW VOLTAGE 2.5 V AND 3.3 V CMOS PLL CLOCK DRIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。