- 您現在的位置:買賣IC網 > PDF目錄45365 > MPC8378VRANGA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 PDF資料下載

參數資料

| 型號: | MPC8378VRANGA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 |

| 封裝: | 31 X 31 MM, 2.46 MM HEIGHT, 1 MM PITCH, LEAD FREE, PLASTIC, BGA-689 |

| 文件頁數: | 72/125頁 |

| 文件大小: | 894K |

| 代理商: | MPC8378VRANGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁當前第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁

MPC8378E PowerQUICC II Pro Processor Hardware Specifications, Rev. 5

Freescale Semiconductor

50

11

Enhanced Secure Digital Host Controller (eSDHC)

This section describes the DC and AC electrical specifications for the eSDHC (SD/MMC) interface of the MPC8378E.

The eSDHC controller always uses the falling edge of the SD_CLK in order to drive the SD_DAT[0:3]/CMD as outputs and

sample the SD_DAT[0:3] as inputs. This behavior is true for both full- and high-speed modes.

Note that this is a non-standard implementation, as the SD card specification assumes that in high-speed mode, data is driven

at the rising edge of the clock.

Due to the special implementation of the eSDHC, there are constraints regarding the clock and data signals propagation delay

on the user board. The constraints are for minimum and maximum delays, as well as skew between the CLK and DAT/CMD

signals.

In full speed mode, there is no need to add special delay on the data or clock signals. The user should make sure to meet the

timing requirements as described further within this document.

If the system is designed to support both high-speed and full-speed cards, the high-speed constraints should be fulfilled. If the

systems is designed to operate up to 25 MHz only, full-speed mode is recommended.

11.1

eSDHC DC Electrical Characteristics

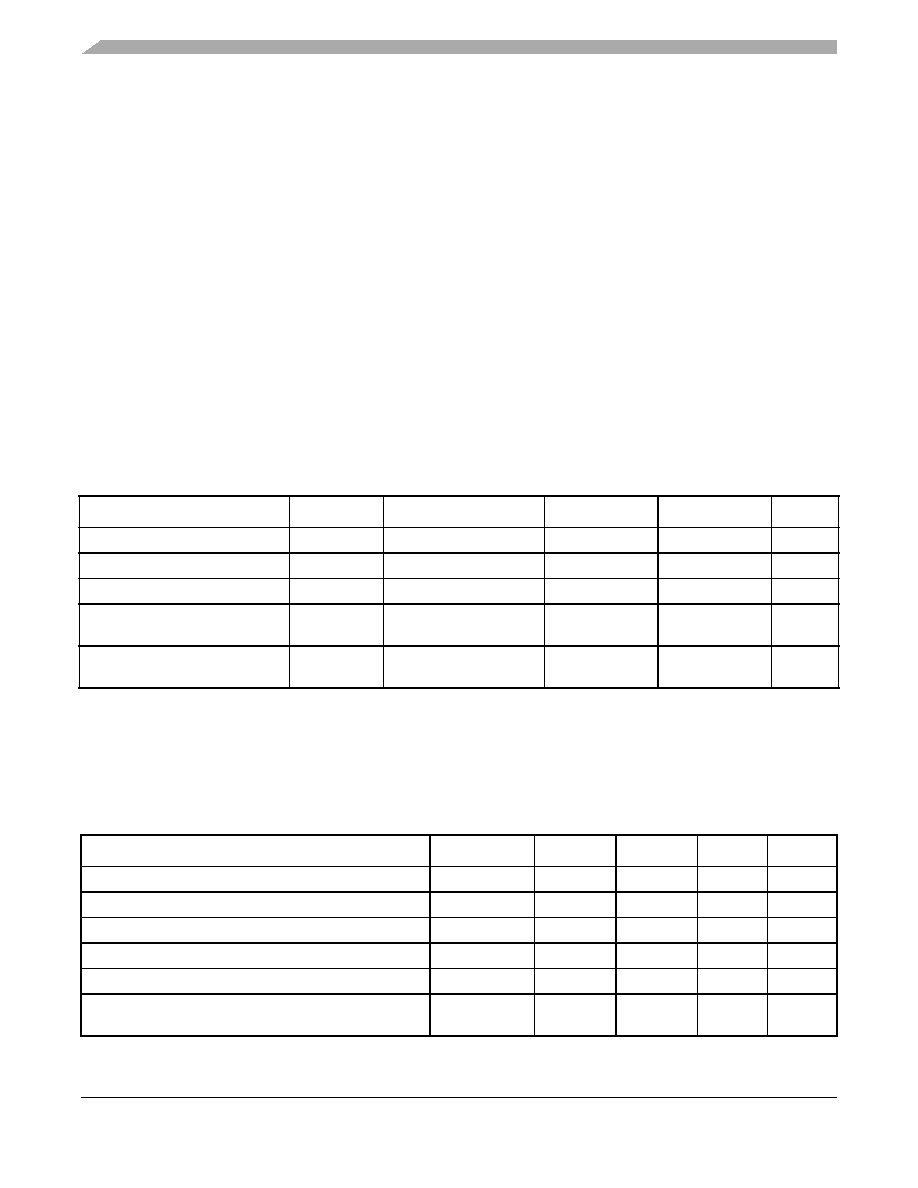

The following table provides the DC electrical characteristics for the eSDHC (SD/MMC) interface of the device.

11.2

eSDHC AC Timing Specifications (Full-Speed Mode)

This section describes the AC electrical specifications for the eSDHC (SD/MMC) interface of the device. The following table

provides the eSDHC AC timing specifications for full-speed mode as defined in Figure 31 and Figure 32.

Table 46. eSDHC interface DC Electrical Characteristics

Parameter

Symbol

Condition

Min

Max

Unit

Input high voltage

VIH

—

0.625

OV

DD

OVDD +0.3

V

Input low voltage

VIL

—

–0.3

0.25

OV

DD

V

Input current

IIN

——

±30

A

Output high voltage

VOH

IOH = –100 uA,

at OVDD(min)

0.75

OV

DD

—V

Output low voltage

VOL

IOL = +100 uA,

at OVDD(min)

—

0.125

OV

DD

V

Table 47. eSDHC AC Timing Specifications for Full-Speed Mode

At recommended operating conditions OVDD = 3.3 V ± 165 mV.

Parameter

Symbol1

Min

Max

Unit

Note

SD_CLK clock frequency—full speed mode

fSFSCK

025

MHz

—

SD_CLK clock cycle

tSFSCK

40

—

ns

—

SD_CLK clock frequency—identification mode

fSIDCK

0400

KHz

—

SD_CLK clock low time

tSFSCKL

15

—

ns

SD_CLK clock high time

tSFSCKH

15

—

ns

SD_CLK clock rise and fall times

tSFSCKR/

tSFSCKF

—5

ns

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8378CVRAJDA | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378ECVRALDA | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378VRAJDA | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378CVRANDA | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378EVRAGFA | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA689 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MPC8378ZQAFDA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8378ZQAFFA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8378ZQAFGA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8378ZQAGDA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8378ZQAGFA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。