- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45333 > ML67Q5003LA (LAPIS SEMICONDUCTOR CO LTD) 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PBGA144 PDF資料下載

參數(shù)資料

| 型號: | ML67Q5003LA |

| 廠商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PBGA144 |

| 封裝: | 11 X 11 MM, 0.80 MM PITCH, PLASTIC, LFBGA-144 |

| 文件頁數(shù): | 3/25頁 |

| 文件大小: | 233K |

| 代理商: | ML67Q5003LA |

FEDL675001-01

OKI Semiconductor

ML675001/67Q5002/67Q5003

10/24

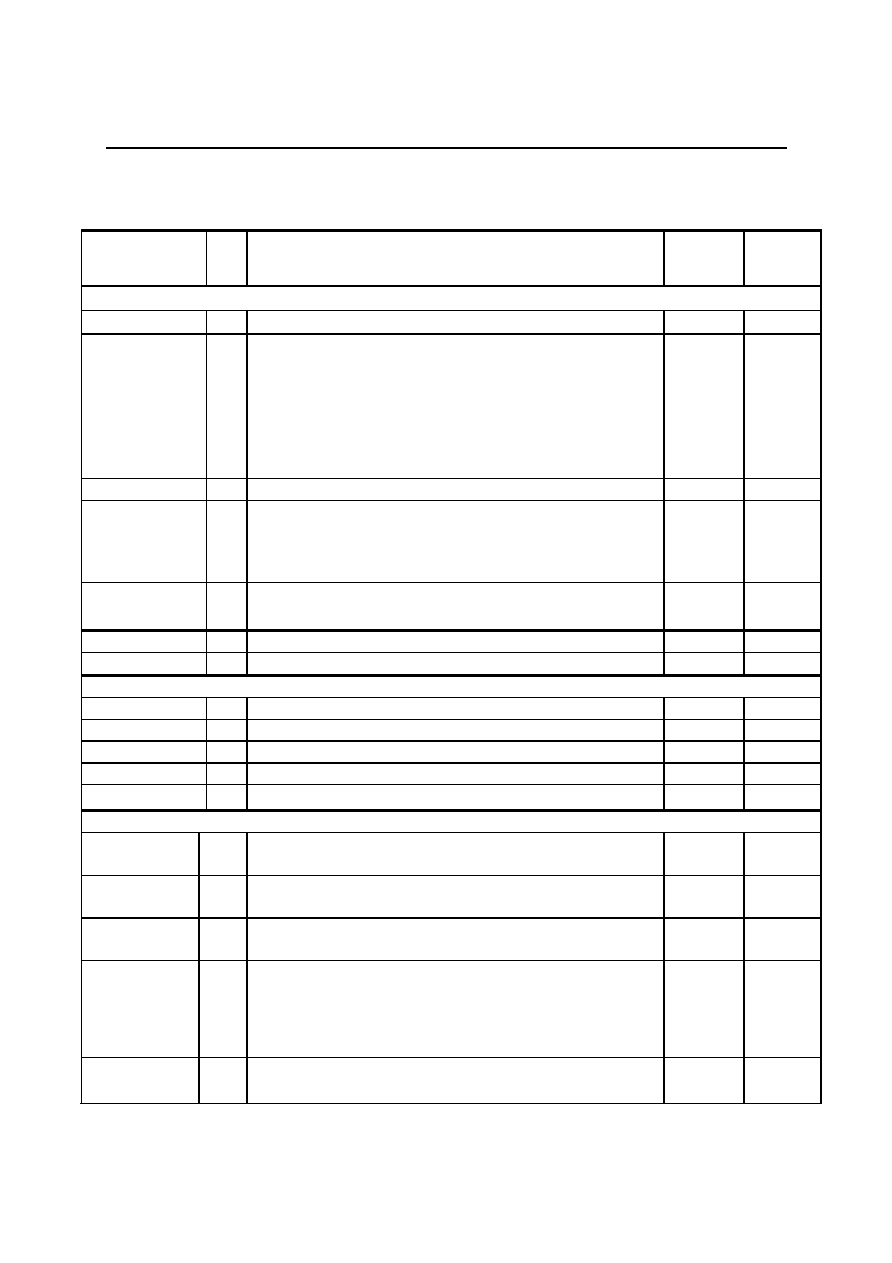

PIN DESCRIPTION

Pin Name

I/O

Description

Primary/

Secondary

Logic

System

RESET_N

I

Reset input

—

Negative

BSEL[1:0]

I

Boot device select signal

BSEL[1] BSEL[0]

Boot device

0

Internal Flash (External ROM for Ml675001)

0

1

External ROM

1

*

Boot mode

The selected device is mapped to BANK0 (0x0000_0000 - 0x07FF_FFFF)

after reset.

—

Positive

CLKMD[1:0]

I

Clock mode input. Normally connect to ground level.

—

Positive

OSC0

I

Crystal connection or external clock input.

Connect a crystal (5MHz to 14 MHz), if used, to OSC0 and OSC1_N.

It is also possible to input a direct clock (5MHz to 14MHz, 20MHz to

56MHz).

—

OSC1_N

O

Crystal connection.

When not using a crystal, leave this pin unconnected.

—

CKO

O

Clock out

—

CKOE_N

I

Clock out enable

—

Negative

Debugging support.

TCK

I

Debugging pin. Normally connect to ground level.

—

TMS

I

Debugging pin. Normally drive at High level.

—

Positive

nTRST

I

Debugging pin. Normally connect to ground level.

—

Negative

TDI

I

Debugging pin. Normally drive at High level.

—

Positive

TDO

O

Debugging pin. Normally leave open.

—

Positive

General-purpose I/O ports

PIOA[7:0]

I/O

General-purpose port.

Not available for use as port pins when secondary functions are in use.

Primary

Positive

PIOB[7:0]

I/O

General-purpose port.

Not available for use as port pins when secondary functions are in use.

Primary

Positive

PIOC[7:0]

I/O

General-purpose port.

Not available for use as port pins when secondary functions are in use.

Primary

Positive

PIOD[7:0]

I/O

General-purpose port.

Not available for use as port pins when secondary functions are in use.

Note that enabling DRAM controller with DRAME_N inputs permanently

configures PIOD[7:0] for their secondary functions, making them

unavailable for use as port pins.

Primary

Positive

PIOE[9:0]

I/O

General-purpose port.

Not available for use as port pins when secondary functions are in use.

Primary

Positive

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML9040-BXXGA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, PQFP80 |

| ML9040A-A01WA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

| ML9040A-AXXWA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

| ML9040A-BXXGA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, PQFP80 |

| ML9040A-AXXWA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML67Q5003-NNNLA | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5003-NNNTC | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5003TC | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5250-NNNLAGZ3A | 制造商:ROHM Semiconductor 功能描述:IC MCU 32BIT 128KB FLSH 144LFBGA |

| ML67Q5260-NNNHBZG3A | 制造商:ROHM Semiconductor 功能描述:DFT BASED FINGERPRINT LSI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。