- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45333 > ML67Q5003LA (LAPIS SEMICONDUCTOR CO LTD) 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PBGA144 PDF資料下載

參數(shù)資料

| 型號(hào): | ML67Q5003LA |

| 廠商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PBGA144 |

| 封裝: | 11 X 11 MM, 0.80 MM PITCH, PLASTIC, LFBGA-144 |

| 文件頁(yè)數(shù): | 25/25頁(yè) |

| 文件大小: | 233K |

| 代理商: | ML67Q5003LA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)

FEDL675001-01

OKI Semiconductor

ML675001/67Q5002/67Q5003

8/24

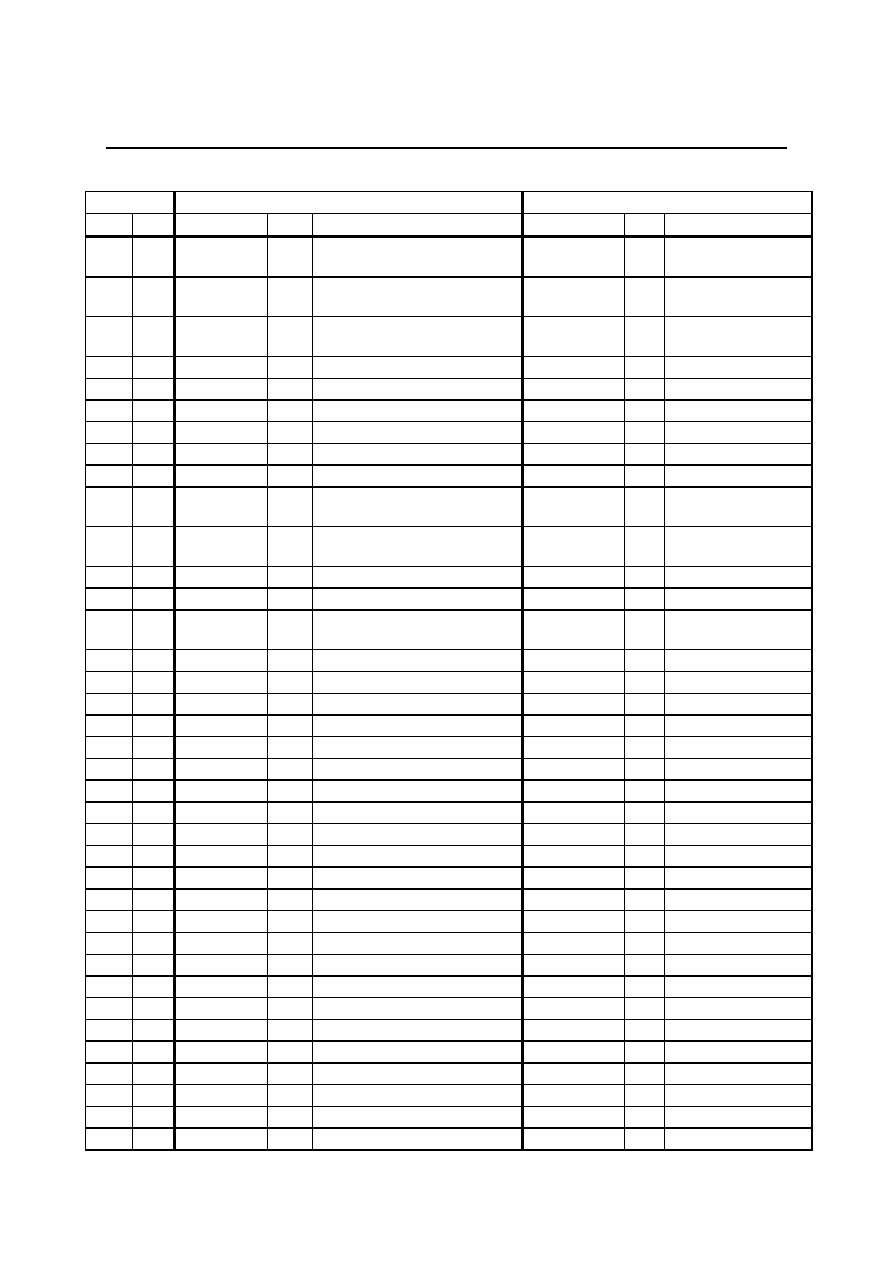

Pin

Primary Function

Secondary Function

LQFP

BGA

Symbol

I/O

Description

Symbol

I/O

Description

79

K13

PIOB[3]

I/O

General port (with interrupt function)

DREQCLR[1]

O

DREQ Clear Signal

(CH1)

80

J11

PIOB[4]

I/O

General port (with interrupt function)

TCOUT[0]

O

DMAC Terminal Count

(CH0)

81

K12

PIOB[5]

I/O

General port (with interrupt function)

TCOUT[1]

O

DMAC Terminal Count

(CH1)

82

J13

PIOC[0]

I/O

General port (with interrupt function)

PWMOUT[0]

O

PWM output (CH0)

83

J10

PIOC[1]

I/O

General port (with interrupt function)

PWMOUT[1]

O

PWM output (CH1)

84

J12

GND

—

85

H13

XBS_N[0]

O

External bus byte select (LSB)

—

86

H12

XBS_N[1]

O

External bus byte select (MSB)

—

87

H10

VDD_CORE

VDD

CORE power supply

—

88

H11

PIOD[0]

I/O

General port (with interrupt function)

XWAIT

I

Wait input signal for I/O

Banks

89

G12

PIOD[1]

I/O

General port (with interrupt function)

XCAS_N

O

Column address strobe

(SDRAM)

90

G10

GND

—

91

G11

VDD_IO

VDD

I/O power supply

—

92

G13

PIOD[2]

I/O

General port (with interrupt function)

XRAS_N

O

Row address strobe

(SDRAM/EDO-DRAM)

93

F11

PIOD[3]

I/O

General port (with interrupt function)

XSDCLK

O

Clock for SDRAM

94

F10

PIOD[4]

I/O

General port (with interrupt function)

XSDCS_N

O

Chip select for SDRAM

95

F12

PIOD[5]

I/O

General port (with interrupt function)

XSDCKE

O

Clock enable (SDRAM)

96

E12

BSEL[0]

I

Select boot device

—

97

F13

BSEL[1]

I

Select boot device

—

98

E10

PIOE[5]

I/O

General port (with interrupt function)

EXINT[0]

I

Interrupt input

99

D12

PIOE[6]

I/O

General port (with interrupt function)

EXINT[1]

I

Interrupt input

100

E13

PIOE[7]

I/O

General port (with interrupt function)

EXINT[2]

I

Interrupt input

101

E11

PIOE[8]

I/O

General port (with interrupt function)

EXINT[3]

I

Interrupt input

102

D11

PIOE[9]

I/O

General port (with interrupt function)

EFIQ_N

I

FIQ input

103

D13

PIOE[0]

I/O

General port (with interrupt function)

SCLK

I/O

SSIO clock

104

C12

PIOE[1]

I/O

General port (with interrupt function)

SDI

I

SSIO Serial Data In

105

D10

PIOE[2]

I/O

General port (with interrupt function)

SDO

O

SSIO Serial Data Out

106

C13

TDI

I

JTAG Data Input

—

107

B12

TDO

O

JTAG data out

—

108

B13

nTRST

I

JTAG reset

—

109

A13

PLLVDD

VDD

Power supply for PLL

—

110

A12

PLLGND

GND

GND for PLL

—

111

C11

CKO

O

Clock output

—

112

A11

JSEL

I

JTAG select

—

113

C10

TMS

I

JTAG mode select

—

114

B11

TCK

I

JTAG clock

—

115

A10

DRAME_N

I

DRAM enable

—

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML9040-BXXGA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, PQFP80 |

| ML9040A-A01WA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

| ML9040A-AXXWA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

| ML9040A-BXXGA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, PQFP80 |

| ML9040A-AXXWA | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC81 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML67Q5003-NNNLA | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5003-NNNTC | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5003TC | 制造商:ROHM Semiconductor 功能描述: |

| ML67Q5250-NNNLAGZ3A | 制造商:ROHM Semiconductor 功能描述:IC MCU 32BIT 128KB FLSH 144LFBGA |

| ML67Q5260-NNNHBZG3A | 制造商:ROHM Semiconductor 功能描述:DFT BASED FINGERPRINT LSI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。