- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45329 > MK20X128VMD100R (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA144 PDF資料下載

參數(shù)資料

| 型號: | MK20X128VMD100R |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA144 |

| 封裝: | 13 X 13 MM, MAPBGA-144 |

| 文件頁數(shù): | 40/74頁 |

| 文件大小: | 1849K |

| 代理商: | MK20X128VMD100R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

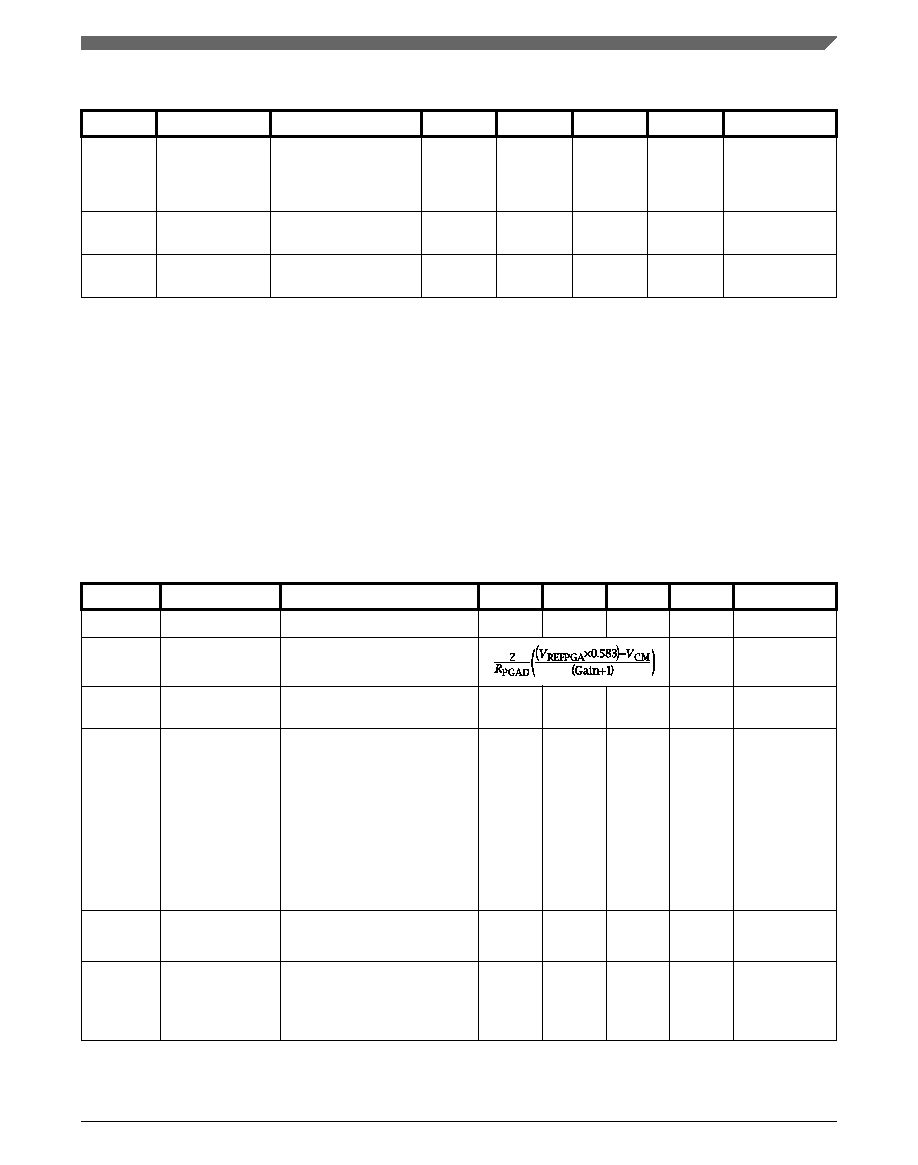

Table 26. 16-bit ADC with PGA operating conditions (continued)

Symbol

Description

Conditions

Min.

Max.

Unit

Notes

RPGAD

Differntial input

impedance

Gain = 1, 2, 4, 8

Gain = 16, 32

Gain = 64

—

128

64

32

—

kΩ

IN+ to IN-4

RAS

Analog source

resistance

—

100

—

Ω

TS

ADC sampling

time

1.25

—

s

1. Typical values assume VDDA = 3.0 V, Temp = 25°C, fADCK = 6 MHz unless otherwise stated. Typical values are for

reference only and are not tested in production.

2. ADC must be configured to use the internal voltage reference (VREFOUT)

3. PGA reference connected to the VREFOUT pin. If the user wishes to drive VREFOUT with a voltage other than the output

of the VREF module, the VREF module must be disabled.

4. For single ended configurations the input impedence of the driven input is 1/2.

5. The analog source resistance (RAS), external to MCU, should be kept as minimum as possible. Increased RAS causes drop

in PGA gain without affecting other performances. This is not dependent on ADC clock frequency.

6. The minimum sampling time is dependent on input signal frequency and ADC mode of operation. A minimum of 1.25s

time should be allowed for Fin=4 kHz at 16-bit differential mode. Recommended ADC setting is: ADLSMP=1, ADLSTS=2 at

8 MHz ADC clock.

6.6.1.4 16-bit ADC with PGA characteristics

Table 27. 16-bit ADC with PGA characteristics

Symbol

Description

Conditions

Min.

Typ.1

Max.

Unit

Notes

IDDA_PGA

Supply current

—

590

TBD

μA

IDC_PGA

Input DC current

A

IILKG

Input Leakage

current

PGA disabled

—

TBD

μA

G

Gain4

PGAG=0

PGAG=1

PGAG=2

PGAG=3

PGAG=4

PGAG=5

PGAG=6

TBD

0.98

1.99

3.97

7.95

15.8

31.4

61.2

TBD

RAS < 100Ω

BW

Input signal

bandwidth

16-bit modes

< 16-bit modes

—

4

40

kHz

PSRR

Power supply

rejection ration

Gain=1

TBD

—

dB

VDDA= 3V

±100mV,

fVDDA= 50Hz,

60Hz

Table continues on the next page...

Peripheral operating requirements and behaviors

K20 Sub-Family Data Sheet Data Sheet, Rev. 4, 3/2011.

Freescale Semiconductor, Inc.

Preliminary

45

相關PDF資料 |

PDF描述 |

|---|---|

| MK20N512VMD100R | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA144 |

| MK20X512VMD100R | RISC MICROCONTROLLER, PBGA144 |

| MK20X512VLQ100R | RISC MICROCONTROLLER, PQFP144 |

| MK2304S-1ILF | 2304 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| MK2304S-1LF | 2304 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MK20X256VLK100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK20X256VLL100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK20X256VLQ100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK20X256VMB100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK20X256VMC100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

發(fā)布緊急采購,3分鐘左右您將得到回復。