- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄201871 > MC68HC11D3CFN3 (FREESCALE SEMICONDUCTOR INC) 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | MC68HC11D3CFN3 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 86/138頁 |

| 文件大?。?/td> | 1047K |

| 代理商: | MC68HC11D3CFN3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當前第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

Interrupts

MC68HC711D3 Data Sheet, Rev. 2.1

Freescale Semiconductor

51

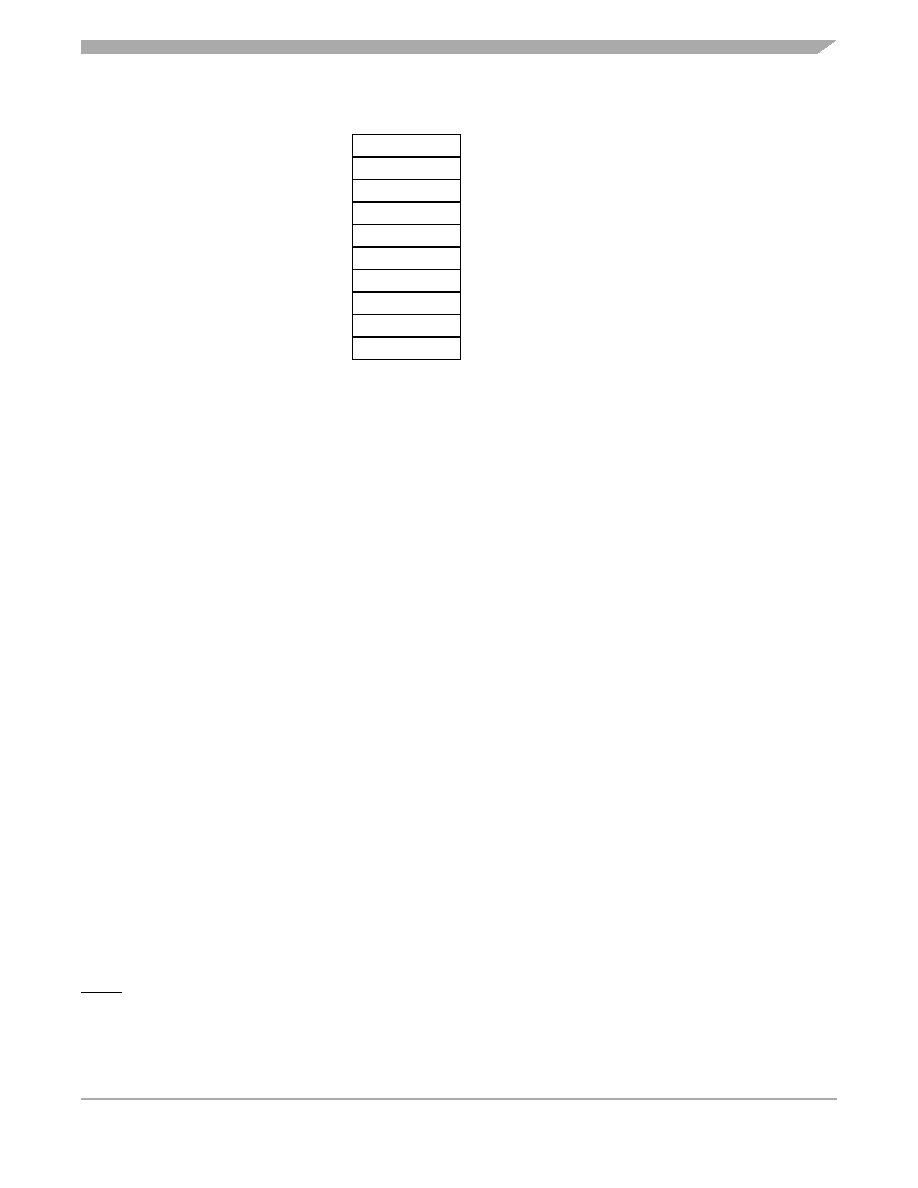

Figure 4-3. Interrupt Stacking Order

4.3.1 Software Interrupt (SWI)

The SWI is executed the same as any other instruction and takes precedence over interrupts only if the

other interrupts are masked (with I and X bits in the CCR set). SWI execution is similar to that of the

maskable interrupts in that it sets the I bit, stacks the central processor unit (CPU) registers, etc.

NOTE

The SWI instruction cannot be executed as long as another interrupt is

pending. However, once the SWI instruction has begun, no other interrupt

can be honored until the first instruction in the SWI service routine is

completed.

4.3.2 Illegal Opcode Trap

Since not all possible opcodes or opcode sequences are defined, an illegal opcode detection circuit has

been included in the MCU. When an illegal opcode is detected, an interrupt is required to the illegal

opcode vector. The illegal opcode vector should never be left uninitialized.

4.3.3 Real-Time Interrupt (RTI)

The real-time interrupt (RTI) provides a programmable periodic interrupt. This interrupt is maskable by

either the I bit in the CCR or the RTI enable (RTII) bit of the timer interrupt mask register 2 (TMSK2). The

rate is based on the MCU E clock and is software selectable to the E

÷ 213, E ÷ 214, E ÷ 215, or E ÷ 216.

See PACTL, TMSK2, and TFLG2 register descriptions in Chapter 8 Programmable Timer for control and

status bit information.

4.3.4 Interrupt Mask Bits in the CCR

Upon reset, both the X bit and I bit of the CCR are set to inhibit all maskable interrupts and XIRQ. After

minimum system initialization, software may clear the X bit by a TAP instruction, thus enabling XIRQ

interrupts. Thereafter software cannot set the X bit. So, an XIRQ interrupt is effectively a non-maskable

interrupt. Since the operation of the I bit related interrupt structure has no effect on the X bit, the internal

XIRQ pin remains effectively non-masked. In the interrupt priority logic, the XIRQ interrupt is a higher

priority than any source that is maskable by the I bit. All I bit related interrupts operate normally with their

own priority relationship.

STACK

SP

PCL

— SP BEFORE INTERRUPT

SP – 1

PCH

SP – 2

IYL

SP – 3

IYH

SP –

4IXL

SP –

5IXH

SP –

6ACCA

SP –

7ACCB

SP –

8CCR

SP –

9

— SP AFTER INTERRUPT

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC08JB1DW | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDSO20 |

| MC68HC08JB1P | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDIP20 |

| MC68HC912BL16FU8 | 16-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 |

| MC68HC912BL16VFU8 | 16-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 |

| MK74CG117AFT | 90 MHz, OTHER CLOCK GENERATOR, PDSO48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11D3CFN4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復。