- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371020 > MC2800 (Motorola, Inc.) FSK FM IF Receiver(FSK FM IF 接收器) PDF資料下載

參數(shù)資料

| 型號(hào): | MC2800 |

| 廠商: | Motorola, Inc. |

| 英文描述: | FSK FM IF Receiver(FSK FM IF 接收器) |

| 中文描述: | FSK信號(hào)調(diào)頻(FSK信號(hào)調(diào)頻中頻接收器中頻接收機(jī)) |

| 文件頁數(shù): | 6/28頁 |

| 文件大?。?/td> | 473K |

| 代理商: | MC2800 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

MC2800

6

MOTOROLA RF/IF DEVICE DATA

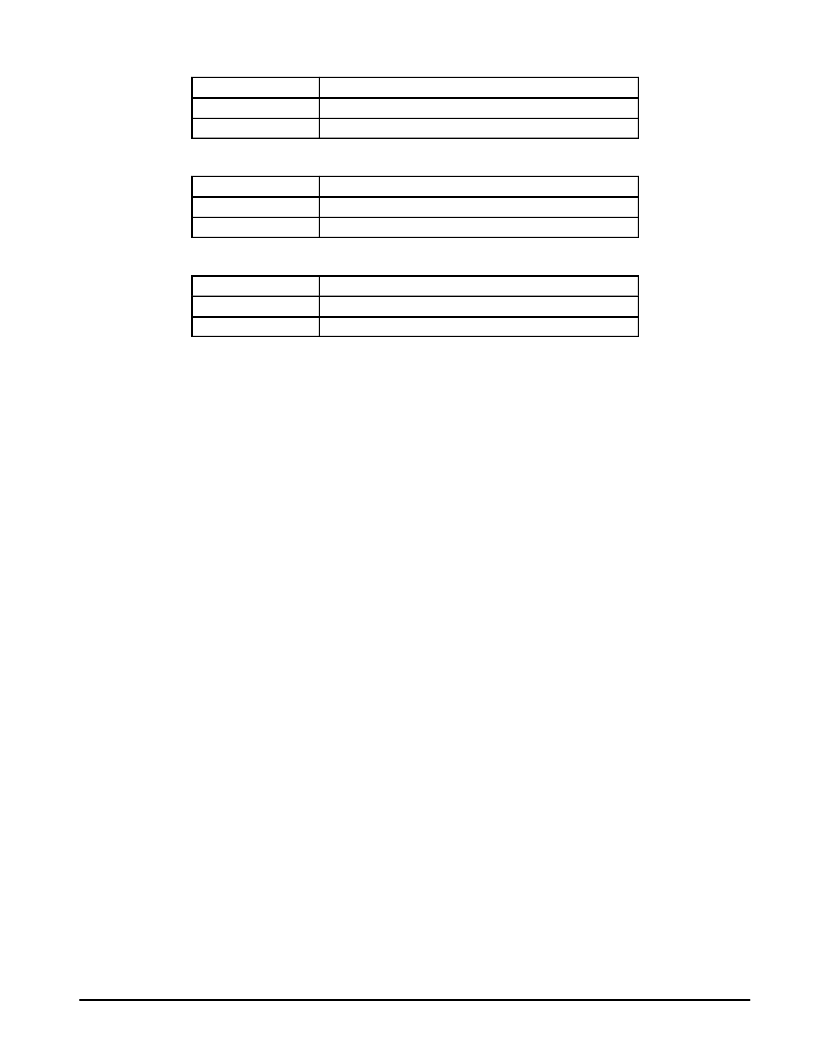

BD Out WITH 100 k

(LOW BATTERY DETECTOR)

BD Out

H

Low Battery

L

–

D1 WITH 100 k

(D1)

D1

H

Dev –4.8 kHz or Dev –1.6 kHz

L

Dev 1.6 kHz or Dev 4.8 kHz

D2 WITH 100 k

(D2)

D2

H

Dev

±

1.6 kHz

L

Dev

±

4.8 kHz

FUNCTIONAL DESCRIPTION

The complete circuit consists of the following functional

blocks as shown in the Block Diagram on page 1.

Oscillator

The oscillator is based on a transistor in common collector

configuration. It requires two external capacitors and a

crystal to form the tank circuit. External capacitors between

base and emitter and from emitter to RF Pwr make the

oscillator transistor to have a negative resistance for small

signals which is the start–up condition for oscillation.

Mixer

The mixer consists of input v–to–i stage and upper

switching stage driven from the oscillator. The LO drive is fed

from the built–in oscillator. The mixer output is obtained at

Mix Out.

IF Amplifier and Limiter

The first ceramic filter is to obtain the 455 kHz IF and to

remove all other harmonics from the mixing process. The

mixer output signal is then amplified in the first IF Amplifier.

The signal is then fed into the second IF Amplifier through the

second ceramic filter. The final IF signal can be monitored at

the limiter output pin Lim Op.

RSSI function

The RSSI function is an indication of the strength of the

incoming signal.

Demodulator

The limiter output @ 455 kHz is fed into the gyrator for

carrier recovery and 90

°

phase shift. This LO signal is then

mixed with the FSK signal fed by the IF Amp for

demodulation. The demodulator output can be obtained at

Det Out.

Bit–Rate Filter

The cut–off frequencies of the filter can be determined by

the 2.2 nF external capacitor between Pins BRF Out and

BRF1, and the 22 nF external capacitor at Pin BRF2. The

filter bandwidth can be switched by Pins R1 and R2 for both

POCSAG and FLEX requirements.

A/D Convertor

The A/D converter features a fully adaptive data slicer. The

input to the converter at Pin BRF Out is initially

peak–detected. Its peak and valley voltages are obtained at

Pins VPk P and VPk N. Three threshold voltages at 1/6, 1/2

and 5/6 of the input signal level are determined dynamically

regardless the actual peak–to–peak value. The final digital

data are obtained at Pins D1 and D2 depending upon the 2 or

4 levels FSK signal.

Low Battery Detector

The battery low indicator senses the supply voltage and

sets its output High when the voltage at input VCC is less than

Vth (typically 1.1 V).

Band Gap Reference

The whole chip can be powered–up and powered–down

by enabling and disabling the band gap reference via the Pin

EN (Enable).

1.0 V Regulator

The 1.0 V voltage at Pin Vreg is used to supply the

regulated voltage for the oscillator and the mixer. It can also

be used to supply other external circuits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC2831A | LOW POWER FM TRANSMITTER SYSTEM SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC2831AD | LOW POWER FM TRANSMITTER SYSTEM SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC2831AP | LOW POWER FM TRANSMITTER SYSTEM SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC3301 | QUAD SINGLE SUPPLY OPERATIONAL AMPLIFIERS |

| MC3401D | QUAD SINGLE SUPPLY OPERATIONAL AMPLIFIERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC2800EVK | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:FLEX Paging RF/IF Receiver Board |

| MC2800SYNEVK | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:FLEX Paging RF/IF Frequency Synthesizer Receiver |

| MC-280B | 制造商:Panasonic Industrial Company 功能描述:BELT |

| MC2820 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Technical Specifications for Brushless Servo Motion Control |

| MC282583 | 制造商:Endicott Research Group Inc (ERG) 功能描述:PANEL; |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。