- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371017 > MC145745FW (MOTOROLA INC) V.21/V.23 Telemeter Modem PDF資料下載

參數(shù)資料

| 型號: | MC145745FW |

| 廠商: | MOTOROLA INC |

| 元件分類: | 調(diào)制器/解調(diào)器 |

| 英文描述: | V.21/V.23 Telemeter Modem |

| 中文描述: | 1.2 kbps DATA, MODEM, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁數(shù): | 3/16頁 |

| 文件大小: | 172K |

| 代理商: | MC145745FW |

MC145745

MOTOROLA

3

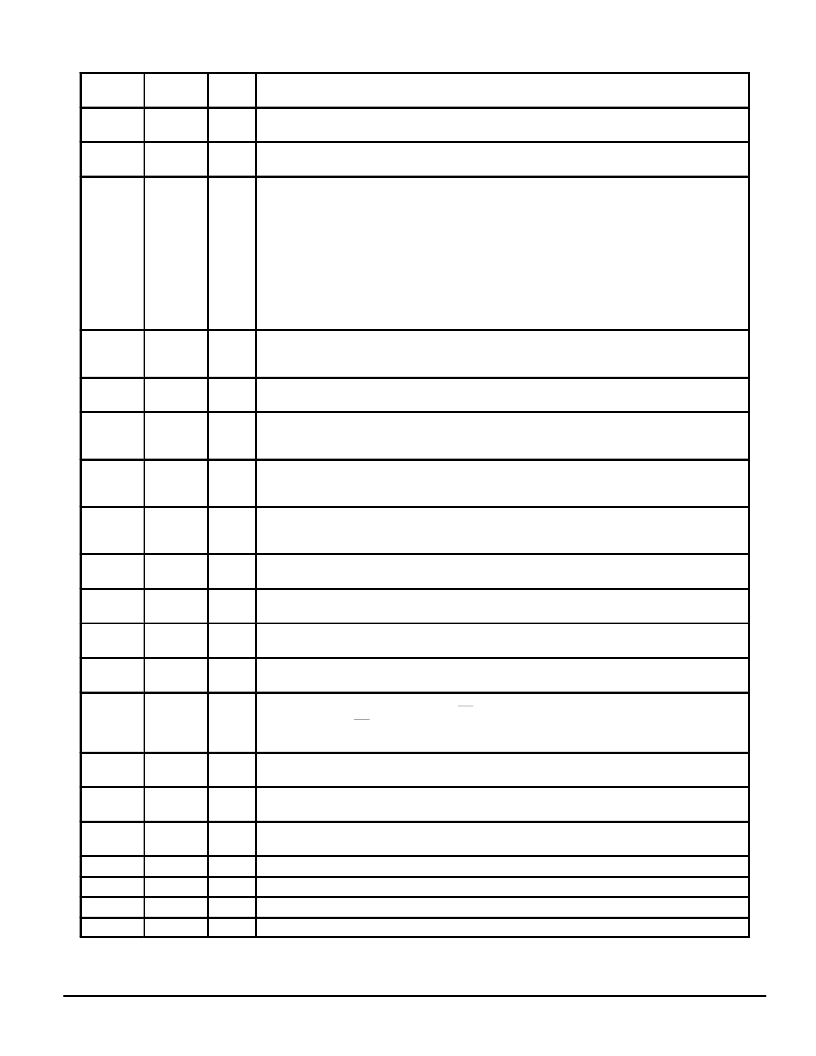

PIN DESCRIPTIONS

Pin

Location

Symbol

Type

Description

1, 14

GND

—

Ground — These are the ground pins of the digital and the analog circuits. The 0 V potential of the

device is determined by the input voltage at these pins.

2

Vref

—

Reference Analog Ground — This pin provides the analog ground voltage VCC/2, which is regulated

internally. This pin should be decoupled to GND with 0.1

μ

F and 100

μ

F capacitors.

3

CDA

—

Carrier Detect Level Adjustment — The detection level for FSK/call–progress tone is determined

according to the voltage at this pin. When VCC = 5 V and the carrier detection level bit (BR3:b1) of the

SCP register is 0, or when VCC = 3.6 V and (BR3:b1) is 1, the CDA voltage is set to 1.25 V by the

internal divider.

This voltage sets the detection levels at ON to OFF: – 44 dBm (typ) and OFF to ON: – 47 dBm (typ).

This high impedance pin should be decoupled to GND with a 0.1

μ

F capacitor.

The carrier detection level is proportional to the terminal voltage at this pin.

An external voltage may be applied to this pin to adjust the carrier detect threshold. The following

equations may be used to find the CDA voltage requirements for a given threshold voltage.

VCDA = 256 x Von

VCDA = 362 x Voff

4

TLA

—

Transmit Level Adjustment — This pin is used to adjust the transmit carrier level which is determined

by the resistor (RTLA) connected between this pin and GND. The maximum level is obtained when

this pin is shorted to GND (RTLA = 0).

5, 24

TEST 1,

TEST 2

I/O

Test Pins 1 and 2 — These test pins are for manufacturer’s use only. These pins should be left open in

normal operation.

6

RxD

O

Receive Data Output — This pin is the receive data output. When the device is in the FSK mode, logic

high on this pin indicates that the mark carrier frequency has been received from RxA, and the logic

low indicates that the space carrier frequency has been received.

7

TxD

I

Transmit Data Input — This pin is the transmit data input. When the device is in the FSK mode, logic

high on this pin generates the mark frequency at TxA1 and TxA2 output, and logic low generates the

space frequency.

8

CD

O

Carrier Detect Output — This pin outputs at low level if a valid FSK, DTMF, or CPTD signal is

received. If the pin is at high level, the receive data output pin (RxD) is internally clamped at high level

to avoid erroneous output of received data caused by line noise.

9

CLKO

O

Clock Output — This pin provides a buffered 3.58 MHz clock output that can drive one CMOS device

such as the MC74HC04.

10

X1

O

Crystal Oscillator Circuit Output — A 3.579545 MHz

±

0.1% crystal oscillator is tied to this pin with the

other end connected to X2.

11

X2

I

Crystal Oscillator Circuit Input — A 3.579545 MHz

±

0.1% crystal oscillator is tied to this pin with the

other end connected to X1. X2 may be driven directly from an appropriate external clock source.

12

ECLK

I

External Clock Input — ECLK is the input of double frequency, 7.159090 MHz

±

0.1%, of the reference

clock. This pin must be connected to GND when not in use.

13

PB0

O

DTMF Receive Data Parallel Output 0 (LSB) — Pins 13, 16, 17, and 18 are the DTMF receive data

valid as long as the CD pin is low. In power down modes 1 and 2, the DTMF receiver is disabled and

these pins are in high impedance.

15, 28

VCC

—

Positive Power Supply — These are the power supply pins for the digital and the analog circuits.

These pins should be decoupled to GND with 0.1

μ

F and 100

μ

F capacitors.

16, 17, 18

PB1, PB2,

PB3

O

DTMF Receive Data Parallel Outputs 1, 2, and 3 (MSB) — These pins are the DTMF receiver data

parallel outputs See pin 13 for more details

parallel outputs. See pin 13 for more details.

19

RESET

I

Reset — A high to low trigger pulse applied to this pin sets all the registers in the default state. It

should remain at high during normal operations.

20

SCP Tx

O

SCP Output Transmit — Refer to

Serial Control Port (SCP Interface)

for additional information.

21

SCP Rx

I

SCP Receive Input — Refer to

Serial Control Port (SCP Interface)

for additional information.

22

SCPCLK

I

SCP Clock — Refer to

Serial Control Port (SCP Interface)

for additional information.

23

SCPEN

I

SCP Enable — Refer to

Serial Control Port (SCP Interface)

for additional information.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145745 | V.21/V.23 Telemeter Modem |

| MC14576AF | Dual Video Amplifiers |

| MC14577CP | Triple Processor Supervisors 20-LCCC -55 to 125 |

| MC14576AP | Dual Video Amplifiers |

| MC14576CP | Automotive Catalog Triple Processor Supervisors 8-SOIC -40 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14574D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC14575CL | 制造商: 功能描述: 制造商:undefined 功能描述: |

| MC14575CP | 制造商: 功能描述: 制造商:Motorola Inc 功能描述: 制造商:undefined 功能描述: |

| MC14576CFEL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC14577CF | 制造商:Freescale Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。