- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369894 > MC12429 (Motorola, Inc.) High Frequency PLL Clock Generator(高頻PLL時(shí)鐘發(fā)生器) PDF資料下載

參數(shù)資料

| 型號(hào): | MC12429 |

| 廠商: | Motorola, Inc. |

| 英文描述: | High Frequency PLL Clock Generator(高頻PLL時(shí)鐘發(fā)生器) |

| 中文描述: | 高頻PLL時(shí)鐘發(fā)生器(高頻鎖相環(huán)時(shí)鐘發(fā)生器) |

| 文件頁(yè)數(shù): | 2/10頁(yè) |

| 文件大小: | 93K |

| 代理商: | MC12429 |

MC12429

MOTOROLA

TIMING SOLUTIONS

BR1333 — Rev 6

2

1

N[1]

N[0]

M[8]

M[7]

M[6]

M[5]

M[4]

XTAL1

NC

NC

PLL–VCC

S_LOAD

S_DATA

S_CLOCK

4

3

2

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

7

8

6

5

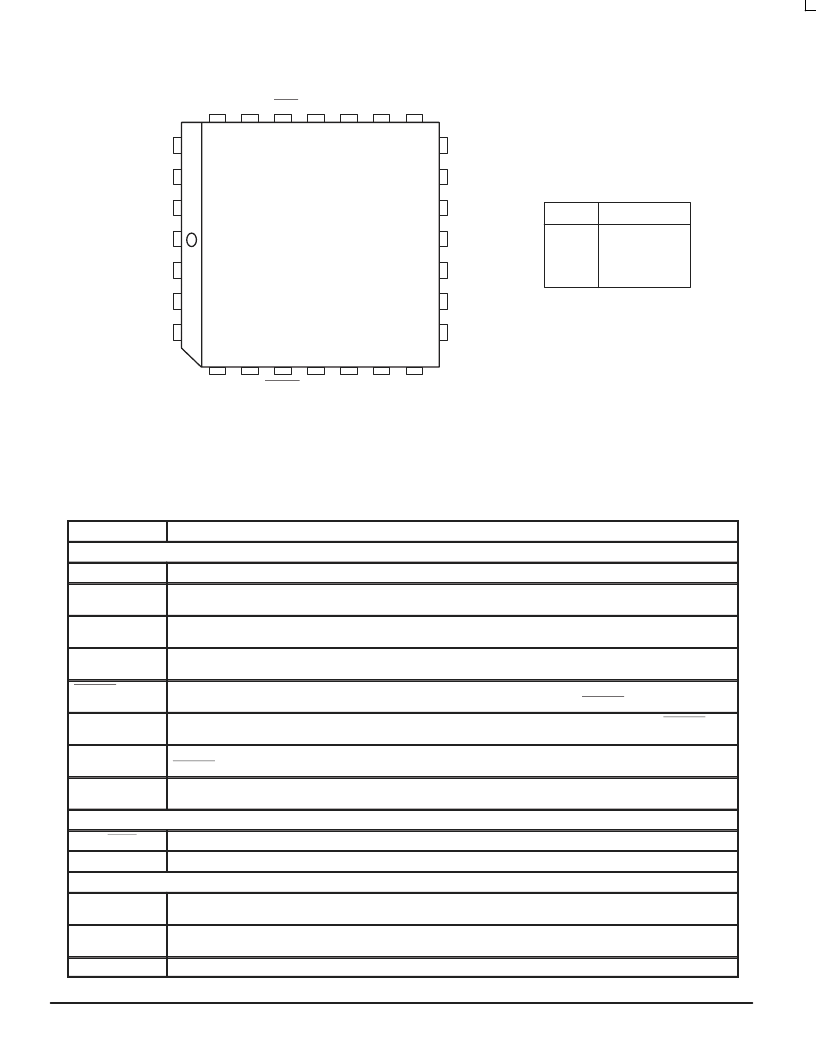

Figure 1. 28–Lead

(Top View)

P_LOAD

VCC

FOUT

FOUT GND

VCC

TEST GND

M[3]

M[2]

M[1]

M[0]

OE

XTAL2

N[1:0]

0 0

0 1

1 0

1 1

Output Division

2

4

8

16

PIN DESCRIPTIONS

Pin Name

Function

Inputs

XTAL1, XTAL2

These pins form an oscillator when connected to an external series–resonant crystal.

S_LOAD

(Int. Pulldown)

This pin loads the configuration latches with the contents of the shift registers. The latches will be transparent when this

signal is HIGH, thus the data must be stable on the HIGH–to–LOW transition of S_LOAD for proper operation.

S_DATA

(Int. Pulldown)

This pin acts as the data input to the serial configuration shift registers.

S_CLOCK

(Int. Pulldown)

This pin serves to clock the serial configuration shift registers. Data from S_DATA is sampled on the rising edge.

P_LOAD

(Int. Pullup)

This pin loads the configuration latches with the contents of the parallel inputs .The latches will be transparent when this

signal is LOW, thus the parallel data must be stable on the LOW–to–HIGH transition of P_LOAD for proper operation.

M[8:0]

(Int. Pullup)

These pins are used to configure the PLL loop divider. They are sampled on the LOW–to–HIGH transition of P_LOAD. M[8]

is the MSB, M[0] is the LSB.

N[1:0]

(Int. Pullup)

These pins are used to configure the output divider modulus. They are sampled on the LOW–to–HIGH transition of

P_LOAD.

OE

(Int. Pullup)

Active HIGH Output Enable. The Enable is synchronous to eliminate possibility of runt pulse generation on the FOUT output.

Outputs

FOUT, FOUT

These differential positive–referenced ECL signals (PECL) are the output of the synthesizer.

TEST

The function of this output is determined by the serial configuration bits T[2:0].

Power

VCC

This is the positive supply for the internal logic and the output buffer of the chip, and is connected to +3.3V or 5.0V

(VCC = PLL_VCC). Current drain through VCC

≈

85mA.

PLL_VCC

This is the positive supply for the PLL, and should be as noise–free as possible for low–jitter operation. This supply is

connected to +3.3V or 5.0V (VCC = PLL_VCC). Current drain through PLL_VCC

≈

15mA.

These pins are the negative supply for the chip and are normally all connected to ground.

GND

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC12430 | High Frequency PLL Clock Generator(高頻PLL時(shí)鐘發(fā)生器) |

| MC13025 | Electronically Tuned Radio Front End |

| MC13028A | C-QUAM AM STEREO ADVANCED WIDE VOLTAGE IF and DECODER for E.T.R. RADIOS |

| MC13109 | Universal Cordless Telephone Subsystem IC |

| MC13109FB | Universal Cordless Telephone Subsystem IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC12429FN | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HIGH FREQUENCY PLL CLOCK GENERATOR |

| MC12430FA | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HIGH FREQUENCY PLL CLOCK GENERATOR |

| MC12430FN | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HIGH FREQUENCY PLL CLOCK GENERATOR |

| MC12439 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HIGH FREQUENCY PLL CLOCK GENERATOR |

| MC12439FN | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:MISCELLANEOUS CLOCK GENERATOR, 28 Pin, Plastic, PLCC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。